Comparison between VHDL and Verilog

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Key Differences

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start by exploring the key differences between VHDL and Verilog. VHDL, being more verbose, offers a strong type system that ensures robustness but can be more complex to write. Can anyone tell me how this might affect your coding experience?

I think it would take longer to write in VHDL, but it might also help prevent errors.

Exactly! On the other hand, Verilog's simpler syntax allows for quicker coding. Student_2, can you think of a scenario where Verilog would be preferable?

In situations where we need to prototype quickly, like testing large-scale systems.

Precisely! Verilog is often the go-to for rapid prototypes. Now, let's summarize this section: VHDL is detailed and robust, while Verilog excels in speed and simplicity.

Choosing the Right Language

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we understand the differences, let's discuss how to choose between them. What factors do you think influence this choice?

Maybe the complexity of the project? If it's simple, we could use Verilog.

And if it's complex, like a detailed simulation, then VHDL would be better!

Exactly right! The ideal choice of language often hinges on the design complexity and specific project needs. Remember, choosing wisely can greatly affect your development efficiency and outcomes!

Application Context

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's apply what we've learned. Can anyone provide a context where VHDL would typically be used and why?

Maybe in defense projects since they require high reliability?

I’ve also heard VHDL is used in academic projects because of its robustness.

Great points! Now how about Verilog? Where do you think it excels?

In commercial chip designs where speed is essential!

Well done! Verilog’s ease of use makes it a favorite for commercial applications, particularly in scenarios that require fast iteration and testing.

In Summary

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up, let's summarize what we've discussed about VHDL and Verilog. Can anyone highlight the major distinctions we covered?

VHDL is more verbose and shifts towards detailed modeling, while Verilog is simpler and faster for prototyping.

Also, the choice depends on factors like design complexity and target applications!

Exactly! Keep these points in mind as they will guide you in your future projects regarding hardware description languages.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses the primary differences between VHDL and Verilog, categorizing their strengths, preferred applications, and guidance for selecting the appropriate language based on specific project needs.

Detailed

Comparison between VHDL and Verilog

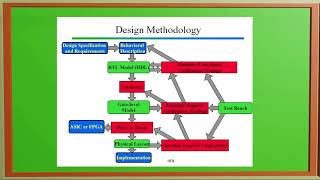

VHDL (VHSIC Hardware Description Language) and Verilog are essential languages in digital design, each offering unique features suited to different applications. In this section, we will explore their contrasting characteristics and assist in determining which language might better meet various design requirements.

Key Differences

- VHDL:

- More verbose and strongly typed, which enhances robustness but requires more code.

- Preferred in academic domains and defense-related projects for high reliability.

- Offers more detailed modeling and can support intricate designs involving various abstraction levels.

- Verilog:

- Features a shorter and simpler syntax, allowing for faster coding and debugging.

- Commonly used in commercial applications, especially in high-performance chip designs where rapid prototyping is essential.

- Ideal for quick simulations of large-scale systems, making it widely adopted in industry settings.

Choosing the Right Language

The decision to use VHDL or Verilog should consider multiple factors such as design complexity, project requirements, and target platforms:

- For smaller, less complex designs, Verilog is typically favored, thanks to its simplicity.

- On the other hand, for more intricate designs that require comprehensive abstraction and detailed simulation, VHDL is often more suitable.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Key Differences

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

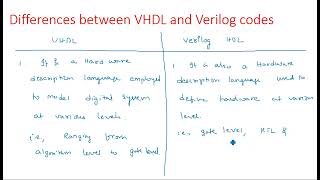

While both VHDL and Verilog are widely used, they have some key differences that influence their application in different domains.

VHDL:

- More verbose and strongly typed.

- Preferred in academic and defense-related projects.

- Supports more detailed modeling and abstraction levels.

Verilog:

- Shorter and simpler syntax.

- More commonly used in commercial applications, particularly in high-performance chip design.

- Easier for quick prototyping and simulation of large-scale systems.

Detailed Explanation

This chunk discusses the fundamental differences between VHDL and Verilog. VHDL is noted for its verbosity and strong typing, which means that it requires more words to express ideas clearly, making it suitable for detailed and complex designs, primarily in academic and defense settings. On the other hand, Verilog has a shorter syntax, which simplifies coding and debugging. It is commonly utilized in commercial sectors, especially in high-performance chip design, allowing for quicker iterations during prototyping and simulation. This difference affects which language engineers choose depending on their project needs and contexts.

Examples & Analogies

Imagine writing a formal report in a job application versus texting a friend. The formal report (VHDL) requires more words and refined structure to clearly convey your skills and experience, acceptable in professional settings. In contrast, a casual text (Verilog) allows you to express your thoughts quickly and spontaneously, focusing more on speed than structure. Similarly, the choice between VHDL and Verilog depends on whether you need detailed documentation or quick code development during a project.

Choosing the Right Language

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The choice between VHDL and Verilog often depends on project requirements, design complexity, and the target platform.

- For smaller or less complex designs, Verilog may be preferred due to its simplicity and faster coding.

- For more intricate designs requiring high levels of abstraction and detailed simulation, VHDL is often the better choice.

Detailed Explanation

This chunk highlights how the decision to use VHDL or Verilog is influenced by the specifics of a project. For projects that are simpler or have fewer design complexities, Verilog is advantageous because its straightforward syntax and quicker coding can speed up the development process. Conversely, if a project involves complex systems that require deep analysis and abstraction or detailed simulation features, VHDL is often more suitable. This understanding helps engineers select the appropriate language based on their immediate needs and long-term objectives in their designs.

Examples & Analogies

Think of cooking a meal. If you're preparing a quick breakfast like cereal (smaller design), you would choose simple steps (e.g., Verilog) that get you there quickly. However, if you're planning a fancy dinner that demands careful preparation and attention to detail (intricate design), you'll follow a detailed recipe (like VHDL) that guides you through complex cooking techniques and requires more time and effort. Just as in cooking, the choice of VHDL or Verilog should match the complexity of the designed circuit.

Key Concepts

-

VHDL: A language that provides strong typing and more verbose syntax for robust designs.

-

Verilog: A simpler, shorter language ideal for quick prototyping and industry applications.

-

Design Complexity: The complexity of a project influences the choice of language.

Examples & Applications

An academic project using VHDL to model a microprocessor for research purposes.

A commercial project utilizing Verilog to design a high-speed network chip.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When you need a lot in detail, choose VHDL without fail. For prototypes and speed indeed, Verilog meets the modern need.

Stories

Once there was a designer named Vicky who loved intricate designs and detailed models. So she always chose VHDL for its rich features. On the other hand, her friend Vince preferred simplicity and speed, thus always picked Verilog for his quick prototypes.

Memory Tools

In a VHDL project, think Create, Control, Check (C3) for complexity management; In Verilog, consider Speed, Simplicity, Success (S3) for fast delivery.

Acronyms

Remember VHSIC for VHDL and VSC (Verilog Simplicity Concept) for Verilog.

Flash Cards

Glossary

- VHDL

VHSIC Hardware Description Language; a strongly typed language used for detailed modeling of digital systems.

- Verilog

A hardware description language known for its simpler syntax, used for both simulation and synthesis of digital circuits.

- FPGA

Field-Programmable Gate Array; a hardware device that can be configured by the user after manufacturing.

- ASIC

Application-Specific Integrated Circuit; a customized integrated circuit designed for a specific use rather than general-purpose use.

Reference links

Supplementary resources to enhance your learning experience.