Choosing the Right Language

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Language Choice

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we will explore how to choose between VHDL and Verilog for your design projects. Why do you think this choice is important?

I think it affects the performance of our designs and how quickly we can develop them.

Exactly! The right language can significantly impact development speed and design complexity. Remember, for less complex designs, Verilog is often the better choice. Can anyone tell me why?

It's simpler and faster to code?

Right! Verilog's succinct syntax allows for quicker prototyping and debugging. It's particularly useful in scenarios where time is of the essence.

But what about when the designs get more complex?

Great question! In those cases, VHDL generally provides better support for detailed modeling and abstraction. It allows for more sophisticated design methodologies that can handle intricate system designs.

That makes sense. So it's really about matching the language to the project's requirements.

Absolutely! Always assess your project requirements and design complexity before making a language choice. Remember the acronym 'SIMPLE' for this. It stands for Simplicity, Intent, Modeling, Performance, Level of detail, and Efficiency.

That’s a helpful way to remember it!

Verilog in Practice

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s dive deeper into Verilog. What types of projects do you think would ideally use Verilog?

Maybe something more straightforward, like a counter or simple ALU?

Exactly! Simple designs like 4-bit counters or basic ALUs can be efficiently built in Verilog due to its straightforward syntax. Can someone give an example of a task where using Verilog would be advantageous?

Testing a small circuit in simulation may be quicker?

Yes! Rapid prototyping is one of its key advantages. Verilog is also more commonly used in industry, so its alignment with commercial applications makes it an excellent choice for simple, large-scale designs.

So even if VHDL may offer more features, Verilog’s simplicity can make it more favorable for quick developments?

Absolutely! Simplicity sometimes trumps complexity for straightforward designs.

When to Choose VHDL

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s consider VHDL. In what scenarios would you choose VHDL over Verilog?

I think for larger, more complex systems that need higher levels of abstraction?

Correct! VHDL is ideal for intricate systems requiring detailed modeling and simulation. Any specific examples of such systems?

Maybe a microprocessor or something like that?

Exactly! Designs such as microprocessors, where precise modeling is critical, benefit from VHDL. Additionally, the strong typing in VHDL can help prevent certain types of errors.

So it's safer for more complex designs?

Well put! The level of detail and verification VHDL can provide makes it very suitable for complex designs. Remember, if your project needs sophistication, you should reach for VHDL!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

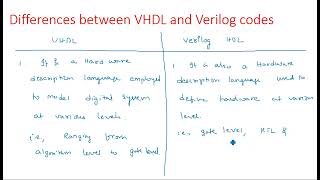

When deciding between VHDL and Verilog, designers should consider factors such as project requirements, design complexity, and the target platform. Verilog is ideal for simpler projects, while VHDL is preferred for intricate designs that require more detailed modeling and simulation.

Detailed

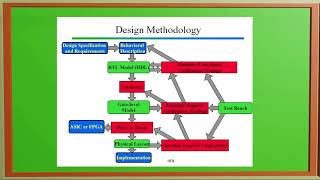

Choosing the Right Language

In digital circuit design, selecting the appropriate hardware description language (HDL) is crucial. This section focuses on VHDL and Verilog, two dominant HDLs, discussing how their characteristics align with various project needs. Designers often opt for Verilog for smaller and less complex designs due to its simplicity, allowing for faster coding and prototyping. Conversely, VHDL is leveraged for intricate projects that demand high abstraction levels and detailed simulations. Understanding these distinctions aids in making informed decisions to optimize design outcomes and resource utilization.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Choosing Based on Design Size and Complexity

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The choice between VHDL and Verilog often depends on project requirements, design complexity, and the target platform.

Detailed Explanation

When deciding whether to use VHDL or Verilog for a project, it's crucial to consider the size and complexity of the design. VHDL is better suited for intricate designs that require detailed abstraction and comprehensive simulation. Its structured format allows designers to model complex systems efficiently. On the other hand, if the project is smaller or less complex, Verilog may be the more appropriate choice due to its simplicity and ease of use. This results in faster coding and more straightforward implementation.

Examples & Analogies

Think of choosing a tool for a job: if you're building a sophisticated piece of furniture (complex design), you might prefer a detailed plan (VHDL) that thoroughly outlines each step. But, if you're just assembling a quick shelf (smaller design), a simple set of instructions (Verilog) will get the job done more efficiently.

Preference for Smaller Designs: Verilog

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

For smaller or less complex designs, Verilog may be preferred due to its simplicity and faster coding.

Detailed Explanation

Verilog is known for its concise syntax, which allows designers to write code quickly compared to VHDL. This speed can be a significant advantage, especially when creating straightforward designs like basic counters or simple logic gates. The language's ease of learning and reduced verbosity make it accessible to beginners or those needing to iterate quickly on projects.

Examples & Analogies

Imagine two chefs in a kitchen: one is preparing a simple sandwich (smaller design) using quick, straightforward steps (Verilog), while the other is crafting a gourmet multi-course meal (complex design) that requires detailed recipes and precise techniques (VHDL). The chef making the sandwich can finish faster due to the simplicity of their task.

Preference for Complex Designs: VHDL

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

For more intricate designs requiring high levels of abstraction and detailed simulation, VHDL is often the better choice.

Detailed Explanation

VHDL shines in scenarios that demand high-level modeling and detailed verification of digital systems. It provides a rich set of features to describe complex behaviors and structures that are beneficial for large-scale projects, such as microprocessors and communication systems. Its strong typing and extensive libraries support sophisticated design requirements, making it the go-to language for many engineers in complex scenarios.

Examples & Analogies

Think of a detailed architectural blueprint (VHDL) for a skyscraper versus a simple drawing (Verilog) for a small house. The skyscraper's blueprint needs to account for various aspects like load-bearing walls, electrical and plumbing systems, and safety features, while the small house can be built with fewer considerations, allowing for greater flexibility and speed.

Key Concepts

-

VHDL: A structured HD language suited for complex designs.

-

Verilog: A concise HD language preferred for simpler applications.

-

Design Complexity: Decides which language is optimal based on project requirements.

Examples & Applications

Design a 4-bit counter in Verilog to understand its simplicity.

Implement a microprocessor in VHDL to leverage its detailed properties.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

VHDL is for the deep and wide, Verilog is quick but won’t provide.

Stories

Imagine a chef selecting a cookware: for a rapid meal, they choose a pan (Verilog). For a gourmet dish requiring finesse, they opt for a pot (VHDL).

Memory Tools

VHDL = Complex, Detail, Lengthy; Verilog = Simple, Swift, Short.

Acronyms

SIMPLE

Simplicity

Intent

Modeling

Performance

Level

Efficiency.

Flash Cards

Glossary

- VHDL

VHSIC Hardware Description Language, used for modeling digital systems at various abstraction levels.

- Verilog

A hardware description language focusing on simplicity and conciseness for circuit design.

- HDL

Hardware Description Language; a specialized language for describing the structure and behavior of electronic circuits.

- Prototyping

The process of creating an early model of a system to test and validate design concepts.

Reference links

Supplementary resources to enhance your learning experience.