Synthesis Issues

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Synthesis Issues

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Alright class, today we're diving into synthesis issues related to VHDL and Verilog. Let's start by defining what synthesis actually means. Can anyone explain?

Isn't synthesis when we convert our code into actual hardware instructions?

Absolutely correct, Student_1! Synthesis translates high-level descriptions into an implemented circuit. Now, what challenges might arise during this process?

Maybe something with resource allocation?

Exactly! Resource allocation issues happen when the synthesizer must fit the model into specific hardware resources. Remember: resources need to be efficiently allocated to avoid unnecessary duplication. Any other challenges?

What about timing constraints?

Great point, Student_3! Timing constraints are critical as they ensure the circuit functions at the required speed. We'll talk about how static timing analysis can be used to mitigate these issues. Let's recap - synthesis is about converting models into hardware, but it must address resource allocation and timing constraints.

Addressing Resource Allocation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about resource allocation. How can we optimize our designs to handle these allocation issues effectively?

We could maybe optimize the design to use fewer resources, like choosing more efficient components?

Exactly, Student_4! Selecting the most resource-efficient components can significantly reduce overhead. Other methods?

What about using design rules or guidelines?

Yes! Following best practices and design guidelines helps ensure your designs are not only efficient but also meet synthesis tool requirements.

How do we assess if we're optimizing well?

Monitoring resource usage during synthesis can provide insights. Remember: control and analyze your resource usage effectively.

Resolving Timing Constraints

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next is timing constraints. Why are they so crucial in our designs?

If our timing isn't right, the circuit might not work correctly.

Exactly, Student_3! It can even lead to circuit failures. So how can we address these timing issues during synthesis?

Using static timing analysis, right?

Precisely! Static timing analysis allows us to identify timing issues without simulating the entire design. It ensures optimal timing is maintained across the board. Recap on this session: timing is vital and can be manage through static timing analysis in VHDL and Verilog designs.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

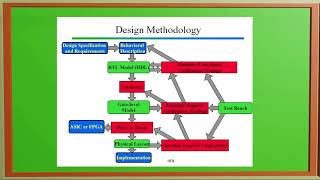

In this section, we explore the synthesis issues that arise while transitioning from simulation to actual hardware implementation in VHDL and Verilog designs. It highlights key design solutions such as utilizing static timing analysis and optimizing designs for specific hardware resources to meet performance constraints.

Detailed

Synthesis Issues in VHDL and Verilog

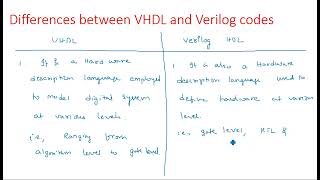

Synthesis refers to the process of converting a high-level hardware description language model into a low-level representation that can be implemented on physical hardware. While simulation validates designs, synthesis can introduce multiple challenges. Key synthesis issues are:

- Resource Allocation: When designs move from simulation to synthesis, synthesizers must allocate physical resources efficiently, which can lead to constraints and optimize specific aspects of the design. This is crucial for ensuring that the final hardware implementation uses available resources properly without redundancy.

- Timing Constraints: Timing is a critical aspect in digital circuit design; thus, designers must ensure that their designs meet speed and performance requirements. This includes analyzing propagation delays, setup, and hold times. Using static timing analysis tools can help identify and resolve timing issues before hardware implementation.

By proactively addressing these synthesis issues through careful design and analysis, designers can significantly improve the performance and reliability of their hardware implementations.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Synthesis Issues

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

While simulation helps validate designs, synthesis tools may introduce issues related to resource allocation and timing constraints.

Detailed Explanation

This chunk discusses the challenges encountered during the synthesis phase of hardware design. Synthesis is the process of converting a high-level hardware description (like VHDL or Verilog) into a lower-level representation that can be physically implemented on hardware. While simulation allows designers to test the functionality of their designs in an ideal scenario, synthesis tools can face problems when mapping that functionality onto the actual hardware resources. Issues that may arise include how effectively resources (like logic gates and flip-flops) are allocated and whether the design will meet timing constraints - that is, can it operate at the required clock speed without errors?

Examples & Analogies

Think of synthesis like preparing a meal based on a recipe (simulation). You might test the taste and look of the dish based on your expectations, but when you start cooking (synthesis), you may face limitations like not having enough ingredients (resource allocation) or burning the food because you didn’t time it right (timing constraints).

Design Solutions for Resource Allocation

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

● Design Solutions:

○ Use static timing analysis to ensure that designs meet performance requirements.

○ Optimize the design for specific hardware constraints like logic utilization and clock speed.

Detailed Explanation

This chunk provides practical solutions to address the synthesis issues mentioned previously. The first solution is to perform static timing analysis, which involves checking the timing of signals in the circuit without needing to simulate the entire design. This helps ensure that all signals arrive at their destinations within the required times to prevent errors. The second solution is to optimize the design itself by considering the limitations of the specific hardware being used. This could mean restructuring how certain operations are implemented to make more efficient use of available logic gates and achieve higher performance with respect to clock speed.

Examples & Analogies

Imagine you are an architect preparing to build a house. Before construction, it’s crucial to review the blueprints (static timing analysis) to ensure everything fits within local building codes (performance requirements). If you find out certain walls are too close together (hardware constraints), you might need to redesign the layout to maximize space and ensure stability (optimization).

Key Concepts

-

Synthesis: The conversion of HDL models into hardware.

-

Static Timing Analysis: A technique to validate timing without simulating entire designs.

-

Resource Allocation: Efficient assignment of resources during synthesis.

-

Timing Constraints: Guidelines ensuring timing integrity in circuit design.

Examples & Applications

An example of synthesis issue could be attempting to fit a complex design into limited FPGA resources without optimizing design elements.

A common timing issue might arise when a circuit’s propagation delay exceeds specified timing constraints leading to malfunction.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Synthesis is quite a feat, turns code to metal, neat and sweet.

Stories

Imagine a baker (synthesizer) turning flour and eggs (HDL code) into delicious cakes (hardware). But if the oven's timing (timing constraints) is off, the cake burns (circuit malfunctions) and no one can eat it.

Memory Tools

S.T.A.R. - Synthesis, Timing Constraints, Allocation, Resource use. Helps remember the critical aspects of synthesis issues.

Acronyms

R.T.A. - Resource Timing Allocation. An acronym for focusing on the main synthesis concerns.

Flash Cards

Glossary

- Synthesis

The process of converting hardware description language models into a physical hardware implementation.

- Static Timing Analysis

A method to ensure that a design meets timing requirements without the need for simulation, identifying delays and critical paths.

- Resource Allocation

The assignment of available resources to various components of a design during synthesis.

- Timing Constraints

Requirements that dictate the maximum and minimum time intervals for circuit operations to ensure proper function.

Reference links

Supplementary resources to enhance your learning experience.