Challenges in VHDL/Verilog Design

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Debugging and Simulation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're delving into debugging and simulation challenges. Can anyone tell me why debugging is particularly challenging in VHDL and Verilog?

I think it's because they are text-based languages, so it's easy to miss errors.

Exactly! Since errors are not always visually obvious, we need robust debugging strategies. One effective method is using simulation tools like ModelSim. What do you think these tools do?

They help us see how our design behaves before we actually build it.

Correct! Using assertions and testbenches can also aid in ensuring that your designs operate as intended. Who can briefly explain what a testbench is?

It's a simulation environment to test the design's inputs and outputs.

Perfect! So remember the important phrase: 'Test early, test often.' This helps catch issues before they become bigger problems. Let's summarize: using simulation tools and implementing testbenches are vital for successful debugging.

Synthesis Issues

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's talk about synthesis issues. Why do you think synthesis can be problematic in our designs?

It's because simulation might show that everything works, but when we synthesize, there could be resource allocation problems.

Very true! Even with correct simulation results, synthesis can introduce timing constraints that are not met. Can anyone name a tool or method used to address these issues?

Static timing analysis helps check if all the timing requirements are satisfied.

Exactly! It’s a powerful way to verify that our designs can run at the required speed. Additionally, we might need to optimize our designs according to specific hardware constraints. What might some of those constraints be?

Logic utilization and clock speed!

Well done! Remembering these constraints helps ensure that our hardware implementations are efficient. In conclusion, understanding and addressing synthesis issues can improve design outcomes significantly.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Challenges encountered during design in VHDL and Verilog primarily revolve around debugging and synthesis. The complex nature of hardware design results in difficulties such as timing constraints and resource allocation problems. Using proper simulation tools and static timing analysis can help mitigate these challenges.

Detailed

Challenges in VHDL/Verilog Design

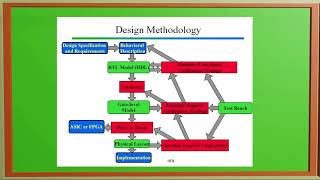

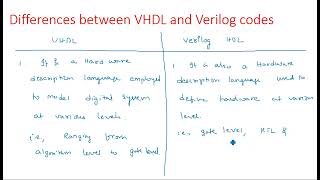

In the design of digital systems using VHDL and Verilog, several challenges arise, particularly concerning debugging, simulation, and synthesis.

Debugging and Simulation

VHDL and Verilog are text-based hardware description languages, which often complicate the debugging process, especially for large designs. Effective debugging strategies include:

- Utilizing simulation tools like ModelSim or Vivado for testing and debugging designs.

- Implementing assertions and comprehensive testbenches to validate the correct operation before physical implementation.

Synthesis Issues

While simulation is crucial for verifying design functionality, it doesn't guarantee that the synthesized hardware will perform correctly. Common synthesis issues include:

- Difficulties in resource allocation which can lead to inefficient designs, and

- Timing constraints that may be violated during synthesis, affecting performance.

To overcome synthesis problems, the following strategies can be employed:

- Conduct static timing analysis to verify that designs meet the necessary performance standards.

- Optimize the design specifically for the hardware platforms being used, taking into account parameters like logic utilization and clock speed.

As designers become more proficient in these languages and the hardware being programmed, these challenges can be managed, leading to successful hardware implementations.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Debugging and Simulation

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

VHDL and Verilog are text-based languages, which can make debugging challenging for large designs.

Design Solutions:

- Use simulation tools such as ModelSim or Vivado to test and debug designs.

- Employ assertions and testbenches to ensure correct operation of the design.

Project Work Example:

Develop a testbench to simulate a complex design, such as a microprocessor, and identify potential errors before hardware implementation.

Detailed Explanation

This chunk discusses the challenges of debugging when working with VHDL and Verilog as text-based languages. When designing large digital circuits, errors are common and can be hard to track. To aid in debugging, simulation tools like ModelSim or Vivado are suggested. These tools allow designers to run their code and check for errors before any physical hardware is created. Additionally, assertions (which are statements that check for specific conditions in the code) and testbenches (a piece of code that applies test cases to the design) help in verifying that the design operates as intended. An example project might involve creating a testbench for a complex design, such as a microprocessor, to identify errors in the code before moving on to production.

Examples & Analogies

Think of debugging a digital design like trying to find a mistake in a large puzzle. When pieces are missing or misplaced (like lines of code), it can be difficult to pinpoint exactly where the error lies. Simulation tools act like a magnifying glass, helping you see the puzzle pieces more clearly and identifying which ones don’t fit. Assertions and testbenches are like asking questions about the puzzle, ensuring each piece fits correctly before you complete the design.

Synthesis Issues

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

While simulation helps validate designs, synthesis tools may introduce issues related to resource allocation and timing constraints.

Design Solutions:

- Use static timing analysis to ensure that designs meet performance requirements.

- Optimize the design for specific hardware constraints like logic utilization and clock speed.

Detailed Explanation

This chunk addresses issues that arise not during simulation but when synthesizing designs for real-world hardware. While simulation can confirm that a design works under ideal conditions, the transition to physical hardware might reveal resource allocation problems (how well the design uses available components) or timing constraints (ensuring signals arrive at the right time). To deal with these challenges, engineers can perform static timing analysis, which checks whether the design meets the necessary speed and performance criteria. Additionally, there’s a focus on optimizing both the design's logic utilization (how efficiently it uses the hardware resources) and its clock speed (how fast it operates).

Examples & Analogies

Imagine preparing a dish in a kitchen. You might follow a recipe perfectly (simulation) and it looks great. Yet, when you actually cook it, you might not have enough oven space, or things might take longer than expected to cook (synthesis issues). Static timing analysis is like checking your oven's temperature and making sure it can handle multiple dishes at the same time efficiently. Optimizing for hardware constraints is similar to arranging your cooking process better or using smaller pots to fit more in the oven.

Key Concepts

-

Debugging: The process of identifying and fixing errors in designs.

-

Static Timing Analysis: Verifies timing constraints to ensure performance.

-

Testbench: Environment to test and validate designs before hardware execution.

Examples & Applications

Using ModelSim to create a testbench for a microprocessor to identify errors in design.

Conducting static timing analysis on an FPGA design to ensure that all timing requirements are met.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Debugging isn't a drag, just let your tools do the swag!

Stories

Imagine you're building a house. You bring in a simulation tool to check if the pipes fit. Before you actually build, you find out the plumbing leaks – that’s your testbench!

Memory Tools

Remember 'DSS' for Debugging - Simulation - Synthesis as the three key challenges.

Acronyms

MUST - ModelSim, Utilize, Synthesize, Test for a successful design process.

Flash Cards

Glossary

- Debugging

The process of identifying and correcting errors in a design or code.

- Simulation

The process of testing the behavior of a design virtually to identify issues before implementation.

- Synthesis

The process of converting the high-level description of a design into a lower-level implementation that can be used on hardware.

- Static Timing Analysis

A method to verify the timing requirements of a design without requiring dynamic simulation.

- Testbench

A simulation environment designed to test a specific design by providing inputs and checking outputs.

Reference links

Supplementary resources to enhance your learning experience.