Key Differences

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding VHDL's Verbosity

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we'll discuss VHDL and its unique features, starting with its verbosity. Who can tell me why verbosity might be beneficial in a programming language?

Maybe it helps avoid errors because everything is clearly defined?

Exactly! VHDL's strong typing allows for rigorous error checking at compile-time, which is essential for complex systems. Can anyone think of a scenario where this might be particularly useful?

In defense projects, where reliability is critical, right?

Yes! In such applications, a failure can have significant consequences, so VHDL's detailed checks are invaluable. Remember, we use the mnemonic 'SURE' – Strong, Understandable, Reliable, Explicit – to highlight these features.

That’s a great way to remember it!

Great! So, VHDL's clarity and structure aids in verification, but how does that compare to Verilog?

Verilog's Simplicity

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s shift our focus to Verilog. How is its syntax different from VHDL?

It’s less verbose and simpler, right?

Correct! This simplicity speeds up the coding process. Can you think of why this might be attractive for commercial applications?

For quick projects or prototypes where time is critical?

Exactly! Verilog shines here; with its quicker learning curve, it's favored for projects like processors. Remember the acronym 'FAST' – Functional, Accurate, Simple, Timely – to sum up these aspects. Why might this simplicity lead to challenges?

Maybe less detail means higher chances of missing critical errors?

Spot on! Balance is key. Recapping, we see that Verilog is excellent for pace but less detailed than VHDL.

Comparing Applications

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s configure how these differences impact our choice when starting a project. What types of projects might benefit from VHDL?

Defense-related projects or complex systems like microprocessors, right?

Exactly! And what about Verilog? When would you choose it?

For smaller or medium designs where we need to prototype rapidly.

Precisely! The choice often hinges on the project’s complexity. Always ask: Do we need precision or speed? To sum it up: VHDL is for detail; Verilog is for speed.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

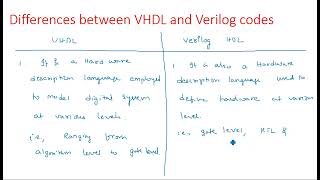

This section discusses the significant differences between VHDL and Verilog, focusing on their verbosity, typing conventions, preferred use cases, and design capabilities. VHDL is often favored for detailed modeling in academic and defense applications, while Verilog's concise syntax makes it ideal for commercial chip designs.

Detailed

Key Differences Between VHDL and Verilog

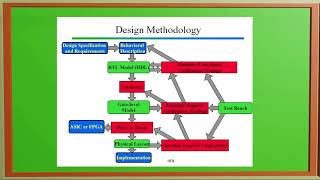

While both VHDL and Verilog are crucial hardware description languages used in digital circuit design, they possess distinct characteristics that cater to various design needs.

- VHDL is known for its verbosity and strong typing, making it suitable for more detailed modeling and ensuring that all variables are explicitly defined and constrained. It is typically preferred in academic circles and defense-related projects where comprehensive simulation and verification are crucial. Moreover, VHDL supports multiple levels of abstraction, allowing engineers to express their designs comprehensively.

- In contrast, Verilog boasts a simpler and shorter syntax, which facilitates quicker coding and debugging. This makes it a popular choice in commercial applications, especially for high-performance chip designs where rapid prototyping is required. Verilog's approach allows designers to focus on functional requirements more swiftly, which suits dynamic design environments better.

Understanding these differences is critical for engineers and students as it helps inform their choice of language based on project requirements and experience level.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of VHDL

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- VHDL:

- More verbose and strongly typed.

- Preferred in academic and defense-related projects.

- Supports more detailed modeling and abstraction levels.

Detailed Explanation

VHDL stands for VHSIC Hardware Description Language. It is known for being more verbose, which means it uses more words and detail compared to Verilog. This strong typing means that the type of data must be explicitly declared, making it clearer and more structured, but it can also require more lines of code to achieve the same functionality. VHDL is often used in academic settings or for projects related to defense because its detailed modeling allows for precise representation of complex systems.

Examples & Analogies

Think of VHDL like writing a detailed recipe for a complex dish. Each step includes precise measurements and instructions, which can be beneficial to ensure success, especially in academic or specialized settings.

Overview of Verilog

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- Verilog:

- Shorter and simpler syntax.

- More commonly used in commercial applications, particularly in high-performance chip design.

- Easier for quick prototyping and simulation of large-scale systems.

Detailed Explanation

Verilog is designed to be shorter and simpler, which means it allows designers to write less code to achieve their goals, making the coding process faster. This language is especially prevalent in the commercial sector, where rapid development and time-to-market are critical, like in the design of high-performance chips. Its ease of use also makes it ideal for quickly simulating and prototyping large systems, saving time during the initial design phases.

Examples & Analogies

Imagine Verilog is like a quick and fluid cooking method, such as stir-frying, where you can throw in ingredients and cook them rapidly without needing extensive preparations. This can be particularly useful in a fast-paced commercial kitchen where speed and efficiency are paramount.

Key Concepts

-

VHDL: A verbose and strongly typed language, favored for detailed, complex designs.

-

Verilog: A simpler, shorter programming language ideal for rapid prototyping in commercial designs.

-

Strong Typing: A characteristic that prevents error through explicit variable definitions.

-

Application Context: Choice of language depends on project requirements and design complexities.

Examples & Applications

VHDL is often used in aerospace projects for simulation due to its detailed error-checking capabilities.

Verilog is commonly utilized in consumer electronics for rapid development cycles.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

VHDL's long, but keeps errors at bay; Verilog's short, gets work done each day.

Stories

Imagine two engineers, one using VHDL, taking time to ensure that every part of the system is thoroughly defined and protected from errors. Meanwhile, the other uses Verilog, quickly iterating over their designs, focusing on getting them functional first. Each chooses according to their project's needs!

Memory Tools

Remember VHDL as 'SURE': Strong, Understandable, Reliable, Explicit.

Acronyms

Think of 'FAST' for Verilog

Functional

Accurate

Simple

Timely.

Flash Cards

Glossary

- VHDL

A strongly typed and verbose hardware description language favored for detailed modeling and academic applications.

- Verilog

A concise hardware description language that is simpler to write and preferred for commercial and large-scale designs.

- Strongly Typed

A programming characteristic where each variable must be explicitly defined to prevent errors.

- Verbosity

The quality of using more words than necessary, often resulting in clearer code.

- Prototype

An initial model used to test and develop ideas quickly.

Reference links

Supplementary resources to enhance your learning experience.