Debugging and Simulation

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Challenges of Debugging in VHDL/Verilog

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to explore the challenges of debugging in VHDL and Verilog. Why do you think debugging is more complicated in these text-based languages?

I think it's because there can be so much code that it's hard to track down errors.

Exactly! Debugging large designs can lead to confusion and inefficiency. So, what strategies can we use to make this process easier?

Maybe using simulation tools like ModelSim?

Right! Tools like ModelSim and Vivado can help simulate and visualize the design. Always remember: **S.M.A.R.T**—Simulation Makes All Reliable Testing!

Let's talk about testbenches. How do you think they help in debugging?

They let you test the design under different conditions.

Correct! Testbenches are vital for validating designs. To wrap up, debugging can be tricky, but tools and methods like simulations and testbenches are invaluable.

Using Assertions for Validation

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's dive deeper into how assertions work in our design process. Has anyone used assertions before?

I've heard they're used to catch unexpected behavior.

Absolutely! Assertions can validate that the design behaves as expected. They help catch mistakes early. Can anyone give an example of how we might use assertions?

Maybe to check that a signal only takes specific values?

Yes! When we assert certain conditions, it ensures that our signals remain within expected parameters. Can everyone remember this acronym for assertions? **C.O.D.E**—Check Output During Execution.

To summarize, using assertions during simulation can dramatically improve the reliability of our designs.

Project Work Example: Developing a Testbench

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's apply what we've learned by developing a testbench. What complexities might we encounter when building one for a microprocessor?

It might be complicated to simulate all the different conditions that the microprocessor will encounter.

Great point! Designing a comprehensive testbench can be challenging because we need to anticipate varied operational scenarios. What strategies can help us in this project?

We can break down the microprocessor into smaller functional blocks.

Exactly! By evaluating each block through our testbench, we can isolate and identify issues more effectively. As a reminder, always follow the approach: **D.E.B.U.G**—Design, Evaluate, Build, Utilize, and Gradually test.

As we move forward, our aim is to identify potential errors efficiently before actual hardware deployment.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The section discusses the complexities of debugging large designs in VHDL and Verilog, recommending the use of simulation tools and testbenches as effective solutions. It highlights the importance of assertions and offers project examples to demonstrate practical applications.

Detailed

Debugging and Simulation

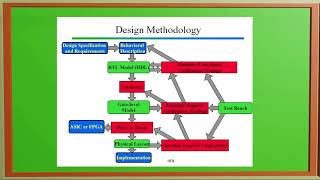

Debugging and simulation are critical aspects of design in VHDL and Verilog, especially as designs grow in complexity. Given that these languages are text-based, debugging can become quite challenging for large designs. Here we identify some effective strategies to mitigate these difficulties:

Design Solutions

- Simulation Tools: Utilizing tools such as ModelSim or Vivado can significantly enhance the testing and debugging processes. These tools provide a detailed environment for simulating designs before implementing them in hardware.

- Assertions and Testbenches: Employing assertions allows designers to validate the expected behaviors of designs. Testbenches serve as setups to simulate the design under various conditions, ensuring it operates correctly.

Project Work Example

A practical way to solidify these concepts is to develop a testbench for a complex design, such as a microprocessor. Through this project, students have the opportunity to uncover potential errors and troubleshoot before moving to hardware implementation. In summary, careful debugging and systematic simulation practices are essential for robust digital circuit design.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Challenges of Debugging in VHDL and Verilog

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

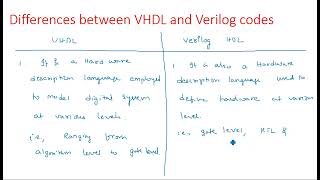

VHDL and Verilog are text-based languages, which can make debugging challenging for large designs.

Detailed Explanation

Debugging is the process of finding and fixing errors in your code. Because both VHDL and Verilog are text-based, it means that you write your designs as lines of code. When you create large systems, like microprocessors or communication circuits, it can be difficult to manually check every part of the code for mistakes or issues. This complexity can make it challenging to ensure that the design will work as intended in real hardware.

Examples & Analogies

Imagine trying to find a typo in a large novel. If it’s only a few pages long, you can read through it quickly and spot errors, but if it’s a massive book, you’d need some help or tools to find those mistakes efficiently. Similarly, with complex VHDL and Verilog designs, having the right tools, like simulation software, can help you identify errors faster.

Solutions for Debugging

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Use simulation tools such as ModelSim or Vivado to test and debug designs.

Detailed Explanation

Simulation tools allow you to run your VHDL or Verilog code in a virtual environment without needing the physical hardware first. This way, you can check how your design behaves when specific inputs are applied. Tools like ModelSim or Vivado provide environments where you can observe the outputs, track signals, and see exactly where things might be going wrong. This is crucial for finding issues before the hardware is built, saving time and resources.

Examples & Analogies

Consider a pilot using a flight simulator to practice flying a plane. The pilot can simulate various scenarios — from perfect conditions to emergencies — without risk. Similar to this, simulation tools allow engineers to explore different scenarios in their designs and catch problems early on.

Utilizing Assertions and Testbenches

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Employ assertions and testbenches to ensure correct operation of the design.

Detailed Explanation

Assertions in the context of VHDL and Verilog are statements that check whether certain conditions hold true while simulating your design. If an assertion fails, it indicates an error. Testbenches are special pieces of code written to simulate inputs and observe outputs, allowing you to validate your design thoroughly. By setting up a testbench with various test cases, you can automate the validation process and make sure your design works under different conditions.

Examples & Analogies

Think of a car safety test where various conditions, such as sudden stops or collisions, are simulated. The car is put through rigorous checks to ensure it's safe in real life. Similarly, testbenches act like safety tests for your designs to ensure they function as expected before being built into hardware.

Project Work Example: Developing a Testbench

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Develop a testbench to simulate a complex design, such as a microprocessor, and identify potential errors before hardware implementation.

Detailed Explanation

In this example, creating a testbench to simulate a microprocessor allows you to systematically check if the microprocessor behaves as expected in response to various instructions and inputs. The testbench runs through different scenarios, checking if the outputs are correct for each set of inputs. This preemptive testing can catch bugs and logical errors, ensuring that when the hardware is eventually made, it operates correctly.

Examples & Analogies

Imagine a recipe for a dish where you practice by making a smaller batch first. You can adjust the ingredients, check flavors, and ensure that everything works well together before making the full meal for a big dinner party. A testbench functions like this practice run, helping ensure the final design has been perfected.

Key Concepts

-

Debugging: The process of finding and fixing bugs in a design.

-

Simulation Tools: Software applications designed to simulate the operation of designs.

-

Testbenches: Frameworks for testing designs through simulation.

-

Assertions: Statements that validate conditions during simulation.

Examples & Applications

Using ModelSim to simulate a VHDL design to identify timing violations.

Creating a testbench in Verilog for a simple adder circuit to verify its operation under various input conditions.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In debugging, take it slow, check the code, and let it flow!

Stories

Imagine a detective (the engineer) using tools (simulation software) to uncover secrets (bugs) hidden in a complex design, solving the case with the help of a trusty sidekick (the testbench).

Memory Tools

Remember S.M.A.R.T for simulation - Simulation Makes All Reliable Testing!

Acronyms

Use **D.E.B.U.G** for the process

Design

Evaluate

Build

Utilize

and Gradually test.

Flash Cards

Glossary

- Debugging

The process of identifying and removing errors from computer hardware or software.

- Simulation Tools

Software used to simulate the behavior of a design before it is physically built.

- Testbenches

Dedicated setups used to test the behavior of a specific design by applying test signals.

- Assertions

Statements in a design that specify certain expected conditions to be true during simulation.

Reference links

Supplementary resources to enhance your learning experience.