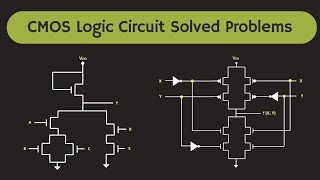

Basic CMOS Logic Gate Structure

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to CMOS Logic Gates

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we will discuss the fundamental building blocks of digital circuits known as CMOS logic gates. Can anyone tell me what CMOS stands for?

I think it stands for Complementary Metal-Oxide-Semiconductor.

Exactly! CMOS technology leverages complementary transistors: NMOS and PMOS. Who can tell me the role of these transistors?

The NMOS conducts when the input is high, and PMOS conducts when the input is low.

Great! This complementary action ensures that while one transistor is on, the other is off, which helps to minimize power consumption. Can anyone explain how this affects the operation of the output?

When NMOS is on, the output goes low, and when PMOS is on, the output goes high.

Exactly! This leads us to how the input signals determine the state of the outputs. Let's summarize the key points: CMOS gates consist of NMOS and PMOS transistors; one is on at any time, minimizing power consumption.

NMOS and PMOS Characteristics

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's now discuss the specific characteristics of NMOS and PMOS. Can anyone tell me the condition for NMOS to conduct?

It conducts when the gate-source voltage is positive or when the input is high.

Correct! And for PMOS?

PMOS conducts when the gate-source voltage is negative, which occurs when the input is low.

Exactly. This complementary nature is what allows us to create various logic functions. Why do you think minimizing power consumption is essential in digital circuits?

It helps in reducing heat generation and increasing overall efficiency.

Great point! So, let’s summarize: NMOS and PMOS conduct under different conditions— this is the basis of how CMOS gates operate.

Output Voltage Control

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's discuss how the output voltage is controlled in a CMOS gate. Who can explain how the output is affected by input signals?

When one transistor is conducting, it drives the output either to the supply voltage or to ground.

Exactly! When NMOS turns on, it pulls the output low, and when PMOS turns on, it pulls the output high. Why is this significant in designing digital circuits?

It allows precise control over the digital signals, which is critical for logic operations.

Right! This precise control is crucial in creating larger, integrated circuits. Let’s summarize: The output is driven high or low based on which transistor is active.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

The structure of CMOS logic gates relies on two types of transistors; NMOS and PMOS. Each transistors conducts under certain conditions, ensuring that while one is on, the other is off, leading to low static power consumption. This section outlines how this complementary action contributes to the driving of output voltages based on input signals.

Detailed

Detailed Summary

In this section, we explore the Basic CMOS Logic Gate Structure, which is pivotal in understanding how digital CMOS logic operates. A CMOS logic gate comprises two complementary transistors: the NMOS and the PMOS. The essential characteristics of these transistors are that:

- NMOS Transistor: It conducts when the gate-source voltage (VGSV_{GS}) is positive, typically activated when the input signal is a high (1).

- PMOS Transistor: It conducts when the gate-source voltage is negative, effectively functioning when the input signal is low (0).

The complementary operation of these transistors has two significant implications:

1. Minimized Static Power Consumption: Only one transistor conducts at any given time, which effectively reduces the static power consumption of the circuit.

2. Output Voltage Control: The output voltage of the logic gate is driven either to the supply voltage (in case of PMOS) or to ground (in case of NMOS), depending on the input signals.

This operational dynamic of CMOS technology is what allows for the integration of multiple logic gates onto a single chip, facilitating the development of complex digital systems.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

CMOS Transistors Overview

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- A CMOS logic gate consists of two transistors of complementary types:

- NMOS transistor: Conducts when the gate-source voltage (VGSV_{GS}) is positive, typically when the input is high (1).

- PMOS transistor: Conducts when the gate-source voltage is negative, typically when the input is low (0).

Detailed Explanation

In a CMOS logic gate, there are two types of transistors used: NMOS and PMOS. The NMOS transistor turns on or conducts electricity when the input voltage is high (1), while the PMOS transistor turns on when the input is low (0). This complementary behavior is crucial for the operation of CMOS gates.

Examples & Analogies

Think of NMOS as a light switch that turns on when the input signal is 'on', while PMOS is like a different kind of switch that turns on when the input signal is 'off'. When one switch is on, the other is off, ensuring energy efficiency in the circuit.

Active Transistor Operation

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

- The complementary action of these transistors ensures that:

- One transistor is on while the other is off, minimizing static power consumption.

- The output voltage will be driven either to the supply voltage (for PMOS) or to ground (for NMOS), based on the input.

Detailed Explanation

The operation of CMOS logic gates is designed such that only one of the two transistors (either NMOS or PMOS) is conducting at any time. This design significantly reduces static power consumption, meaning that power is not wasted when the gate is not switching. Depending on the state of the inputs, the output voltage will either be pulled up to the supply voltage by the PMOS transistor or pulled down to ground by the NMOS transistor.

Examples & Analogies

Imagine a seesaw where one side (the NMOS) goes down to ground while the other side (the PMOS) lifts to the top, but they never move together. This movement saves energy, much like how a well-designed car engine operates efficiently by not wasting fuel.

Key Concepts

-

CMOS Gate Structure: CMOS logic gates use NMOS and PMOS transistors for complementary operation.

-

Power Consumption: CMOS gates minimize static power usage by ensuring only one transistor conducts at a time.

-

Output Control: The output is determined by the active transistor based on input signals.

Examples & Applications

If the input signal is 1, the NMOS turns on, grounding the output at 0.

If the input signal is 0, the PMOS turns on, pulling the output to Vdd, creating an output of 1.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

NMOS conducts with a positive tide, while PMOS by negative voltage will glide.

Stories

Imagine a dance where two partners, NMOS and PMOS, perform in perfect harmony. When one leads (conducts), the other follows (doesn't conduct), thus beautifully minimizing energy use while dancing through digital logic.

Memory Tools

Remember: NMOS = Needs More On Signal; PMOS = Pulls When More Off Signal.

Acronyms

Think of CPMO

Control by PMOS or NMOS Output!

Flash Cards

Glossary

- CMOS

Complementary Metal-Oxide-Semiconductor, a technology for constructing integrated circuits.

- NMOS

A type of transistor that conducts when the gate-source voltage is positive.

- PMOS

A type of transistor that conducts when the gate-source voltage is negative.

- Static Power Consumption

Power used by a circuit when not switching states.

Reference links

Supplementary resources to enhance your learning experience.