Design of Combinational Circuits using Verilog

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Verilog Syntax

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're diving into the design of combinational circuits using Verilog, focusing on the AND gate. Can someone tell me what an AND gate does?

It outputs true only when both inputs are true.

Exactly! Now, let's look at how we can implement this in Verilog. Here's the module definition for a 2-input AND gate: `module and_gate(input A, input B, output Y);` Can anyone tell me why 'input' and 'output' are used here?

They define what signals the module will receive and send out.

Great job! Next, we have the statement `assign Y = A & B;`. Can anyone explain what this operation is doing?

It assigns the logical AND of A and B to Y.

Well done! This is fundamental in understanding how digital logic can be represented through Verilog.

Building on the AND Gate Example

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now that we understand how to code an AND gate, let’s think bigger. What applications can you think of that utilizes AND gates?

They are used in circuits like adders and in controlling logic!?

Exactly! These are foundational elements in complex circuits. Remember, the AND gate is one of the basic building blocks of combinational logic! What about the structure? Can you relate it to any programming concepts?

It’s similar to a function that returns a value based on given inputs!

Very accurate! So, as you create more complex circuits, you'll be layering these simple functions together. Always think of these modules as functions in programming.

Practice and Apply What You've Learned

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s apply what we’ve learned. I want each of you to write a simple Verilog code for an OR gate. Who can remind us what an OR gate does?

It outputs true if at least one of the inputs is true.

Perfect! Now, try to write the module with the correct syntax. Don’t forget about the assignment statement for the OR operation.

I think I have it! `module or_gate(input A, input B, output Y); assign Y = A | B;`

Excellent! You've just recreated another foundational logic gate in Verilog. Understanding these basics sets the stage for designing more complex circuits.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

In this section, we explore the design of combinational circuits with Verilog, starting with a clear example of a 2-input AND gate. We discuss the structure and syntax of module declarations, input-output specifications, and the assignment statement for logical operations.

Detailed

Design of Combinational Circuits using Verilog

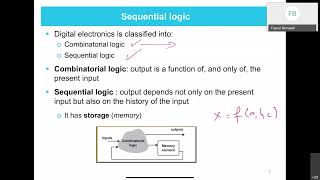

Combinational circuits are vital components in digital systems, and their design using hardware description languages (HDLs) like Verilog is an essential skill for engineers. In this section, we focus on crafting a 2-input AND gate using Verilog.

The Verilog code begins with a module declaration that outlines the inputs and outputs of the AND gate. The syntax used is structured as follows:

This snippet showcases key components of Verilog design:

- Module Declaration: The module keyword defines the start of a block that groups related components and functionality.

- Input/Output Specification: Inputs and outputs are clearly defined, allowing for straightforward interfacing.

- Assignment Statement: The logical operation is performed using the assign keyword, showing how the output Y is assigned the result of the AND operation between inputs A and B.

Thus, using Verilog, designers can effectively implement various combinational circuits that respond systematically to input changes, leveraging the succinctness and clarity of this HDL.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Module Declaration

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

module and_gate( input A, // Input A input B, // Input B output Y // Output Y );

Detailed Explanation

This chunk introduces the module declaration for a 2-input AND gate in Verilog. In Verilog, a module is a basic building block of a design, similar to a function in programming. The module keyword starts the declaration, specifying the name of the module (and_gate). Within the parentheses, we define the inputs and the output. Here, input A and input B are defined as inputs, while output Y is defined as the output of the module.

Examples & Analogies

Think of the module as the blueprint of a house. The inputs (A and B) can be compared to inputs like electricity and plumbing systems—essential for the house to function, while the output (Y) is the final product that your house offers—like a comfortable living space.

AND Operation Assignment

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

assign Y = A & B; // AND operation endmodule

Detailed Explanation

This chunk focuses on how the output of the AND gate is defined in Verilog. The assign statement is used to calculate the output. Here we see Y = A & B, where the & operator represents the AND logic operation. This means that the output Y will only be true (1) if both inputs A and B are true (1). The endmodule keyword signifies the end of the module declaration.

Examples & Analogies

Imagine two light switches in a room. The AND operation means that both switches need to be ON for the light (output Y) to be ON. If either switch is OFF, the light remains OFF.

Key Concepts

-

Verilog: A HDL used for designing digital circuits.

-

Module: A self-contained component in Verilog, defining inputs and outputs.

-

AND Gate: A fundamental combinational circuit whose output is true when all its inputs are true.

-

Assign Statement: A Verilog command that defines how outputs are calculated from inputs.

Examples & Applications

2-input AND gate implemented in Verilog, showing module structure and syntax.

An OR gate designed similarly to reinforce understanding.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To make output bright and true, both inputs must shine through.

Stories

Imagine a light switch - it only turns on when both switches are on. That's how an AND gate operates!

Memory Tools

A(n) AND gate = A & B = Always needs Both inputs true.

Acronyms

AND

= A

= Needs

= Dual input true.

Flash Cards

Glossary

- Verilog

A hardware description language (HDL) used for modeling electronic systems.

- Module

A basic building block in Verilog containing inputs, outputs, and internal logic.

- Assign Statement

A command in Verilog used to define how output values are computed from inputs.

- AND Gate

A digital logic gate that outputs true only if both inputs are true.

- Input/Output

Signals through which the module communicates with its environment.

Reference links

Supplementary resources to enhance your learning experience.