Placement and Routing Co-Optimization

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Co-Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we will discuss co-optimization in VLSI design, particularly how placement and routing affect overall performance. Why do you think these two aspects are related?

I think if the placement is poor, the routing will also be affected, leading to longer wire lengths?

Exactly! Longer wires can lead to delays and higher power consumption. This is where timing-driven placement comes into play.

What do you mean by timing-driven placement?

Timing-driven placement focuses on putting cells that are part of the critical path closer together to minimize delay. Great observation!

So, better placement can help improve timing performance, right?

Absolutely! And we'll explore how that ties into power-aware strategies next.

Timing-Driven Placement

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's focus on timing-driven placement. Students, what factors do you think influence the placement of elements based on timing?

The critical path and the delays associated with different cells?

Correct! We want to minimize the delays associated with those critical paths. By positioning cells optimally, we enhance performance.

How does it actually minimize delays?

By reducing wire lengths between critical cells, we decrease the resistance and capacitance, leading to faster signal propagation. Does everyone understand that connection?

Yes, timing is crucial for performance.

Power-Aware Strategies

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

The next aspect we will discuss is power-aware placement and routing. How might addressing power consumption influence our design?

It reduces the overall power draw, especially for battery-operated devices!

Exactly! When we place power-efficient cells near each other and optimize routing paths to be shorter, we also tackle power dissipation effectively.

What happens if we don't consider power during placement and routing?

Ignoring power can lead to higher heat output, inefficiency, and potentially failing designs, especially in mobile devices.

Got it! So, co-optimization isn't just about performance; it's also about efficiency!

Correct! Let's summarize what we've discussed today.

Recap and Q&A

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

To wrap up, we have learned about timing-driven placement and power-aware strategies. Can someone summarize the key benefits of co-optimization?

It minimizes delays and power usage while improving overall circuit performance.

And placing critical components efficiently is crucial for achieving these goals.

Fantastic! Any final questions or thoughts?

What tools can we use for these co-optimization strategies?

Many modern EDA tools integrate these strategies to facilitate placement and routing, helping engineers achieve better results.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses the importance of co-optimizing placement and routing in physical design, detailing techniques like timing-driven placement and power-aware strategies that lead to improvements in wirelength, timing, and power consumption.

Detailed

Placement and Routing Co-Optimization

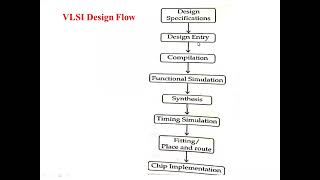

Placement and routing are critical steps in the physical design of VLSI circuits. Optimizing these processes together—referred to as co-optimization—can yield significant improvements in various performance metrics.

Key Techniques:

- Timing-Driven Placement: This technique focuses on strategically placing cells based on timing needs, ensuring that components along the critical path are located closer together to minimize signal delay. By prioritizing the placement according to timing requirements, the overall performance of the circuit can be enhanced significantly.

- Power-Aware Placement and Routing: This approach considers both cell placement and routing strategies with an eye towards reducing power consumption. Cells that consume less power are placed near each other, and the routing design aims to minimize length and power dissipation, leading to a more efficient design.

The integration of these methodologies represents a critical advancement in physical design, allowing for simultaneous optimization of timing and power—a necessity in modern VLSI design.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Co-Optimization

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Placement and routing are closely related steps in physical design, and optimizing them together can yield better results. Co-optimization techniques ensure that the placement and routing decisions work together to minimize wirelength, improve timing, and reduce power consumption.

Detailed Explanation

This chunk introduces the concept of co-optimization in physical design, where the processes of placement and routing are done in conjunction. By considering both aspects together, designers can make more informed decisions that lead to lower wirelength, better timing performance, and reduced power usage. Essentially, the goal is to optimize these two interconnected processes simultaneously rather than treating them as separate tasks.

Examples & Analogies

Imagine a city planner who is designing a park and the surrounding roads. If the planner optimizes the park's location without considering where the roads will go, it could lead to longer drive times and wasted space. However, if the planner optimizes both the park's placement and the road layout together, they can create a more efficient and enjoyable city layout.

Timing-Driven Placement

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

In this approach, placement is optimized based on the timing requirements of the design. Cells that are part of the critical path are placed closer to minimize delay, while less critical cells are placed in less constrained regions.

Detailed Explanation

Timing-driven placement is a technique where the arrangement of cells is done with timing in mind. The critical path represents the longest sequence of dependent tasks in a circuit, and any delays along this path can negatively impact the circuit's performance. By placing critical cells closer together, designers can reduce the distance signals must travel, thus minimizing timing delays. Cells that are not critical can be positioned in less impactful areas, allowing designers to optimize the overall layout effectively.

Examples & Analogies

Consider a relay race where runners pass a baton. If the runner passing the baton stands too far from the next runner, it wastes time during the exchange. If they stand close together, the baton passes quickly, improving the race time. Similarly, placing critical cells close together in timing-driven placement accelerates data transfer within the circuit.

Power-Aware Placement and Routing

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Co-optimizing power-aware placement and routing ensures that both the placement of cells and the routing of wires take power consumption into account. By placing cells with lower power consumption near each other and routing signals efficiently, overall power consumption can be reduced.

Detailed Explanation

Power-aware placement and routing is a vital strategy focusing on reducing power consumption in the design. By strategically placing cells that use lower power in proximity to one another, and then routing connections in a way that minimizes power-wasting paths, designers can achieve a more energy-efficient layout. This aspect of co-optimization can significantly impact device longevity and thermal performance, which are crucial in modern VLSI design.

Examples & Analogies

Think of a group of friends who are trying to save money on a group trip. If everyone sits in the same car instead of taking multiple cars, they save on fuel, which is more efficient. Similarly, by placing low-power cells together and optimizing their connections, the circuit can operate more efficiently and consume less power.

Key Concepts

-

Co-Optimization: The integration of placement and routing to enhance circuit performance.

-

Critical Path: The sequence of stages determining the minimum time needed for an operation in a circuit.

Examples & Applications

In a chip design where the placement of logic gates is performed without considering routing, wire lengths can be excessively long, leading to delayed signals and greater power consumption.

Conversely, co-optimizing placement based on critical paths and efficient routing results in shorter wire lengths and faster signal propagation.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

For placement tight and routing bright, combine them both, and do it right.

Stories

Imagine you are building a toy train track where you want the trains to go fast. If you put pieces too far apart, the train slows down. But if you place them closely, it zooms without delay. This is how timing-driven placement works!

Memory Tools

P.R.I.M.E. for co-optimization: Placement, Routing, Integrated, Minimize power and Energy.

Acronyms

C.P.R. for critical paths in routing

Critical Placement Rationality.

Flash Cards

Glossary

- TimingDriven Placement

Placement strategy that arranges components based on timing requirements to minimize delays.

- PowerAware Placement

Placement and routing methodology considering power consumption to enhance design efficiency.

Reference links

Supplementary resources to enhance your learning experience.