Wirelength Minimization

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Importance of Wirelength Minimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to discuss wirelength minimization. Can anyone tell me why wirelength is an important factor in VLSI design?

I think shorter wires can help reduce signal delay, right?

Exactly, Student_1! Shorter wires reduce the time it takes for signals to travel. Longer wires not only increase delay but also increase power consumption.

Is there a specific reason why longer wires consume more power?

Great question, Student_2! Longer wires have higher resistance and capacitance, which means they dissipate more energy when charges pass through. This forms the basis of why minimizing wire length is crucial.

Let's remember this concept with the acronym 'WAVE' - Wires Add to Voltage Excess.

So, if we minimize wirelength, we can keep both delay and power consumption in check?

Precisely, Student_3! By keeping wirelength minimized, we enhance performance and efficiency throughout the chip.

To recap, minimizing wirelength reduces signal delays and power consumption. Moving on, let’s discuss the challenges related to routing congestion.

Challenges in Routing Congestion

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

What do you think could happen if there's too much routing congestion on a chip?

I assume it could lead to delays, kind of like traffic jams.

That's right, Student_4! Just like traffic jams slow down vehicles, routing congestion can delay signal transmission, leading to performance issues.

Is congestion a common problem in VLSI design?

Yes, it’s a critical challenge! Designers must balance routing paths to avoid congestion, ensuring smooth signal flow.

How do designers typically tackle this issue?

Excellent question! They can use advanced algorithms to optimize paths, prioritizing minimal wire connections while utilizing multiple layers for routing.

Let’s summarize: Routing congestion can severely impact performance, but using effective algorithms can help mitigate this problem.

Techniques for Wirelength Minimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s delve into techniques for minimizing wirelength. Can anyone suggest methods engineers use?

Maybe using the shortest path algorithms?

Great point, Student_3! Shortest path algorithms are vital for finding optimal routing paths. They help minimize wirelength effectively.

What about using multiple layers? Does that help too?

Absolutely! Multi-layer routing allows for greater flexibility, reducing congestion and optimizing connections.

Would implementing these methods always guarantee better performance?

Not necessarily, Student_1. While these techniques significantly reduce wirelength and improve performance, careful balancing of other factors, like power and timing, is essential.

In summary, effective techniques like shortest path algorithms and multi-layer routing are crucial for successful wirelength minimization.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

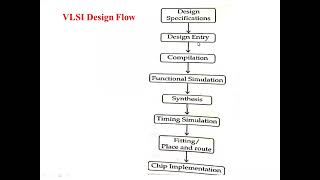

This section discusses wirelength minimization within the context of routing optimization strategies in VLSI design. It highlights the importance of minimizing wirelength to enhance circuit performance, such as reducing delay and power consumption while addressing challenges in routing congestion.

Detailed

Wirelength Minimization

Wirelength minimization is a significant aspect of routing optimization in VLSI design. The primary goal is to reduce the total length of wires connecting various components on the chip, which directly influences both the performance and power requirements of the circuit. By ensuring shorter wire connections, designers can achieve a lower delay in signal propagation, leading to improved timing performance.

Key Points Covered:

- Impact of Wirelength on Performance: Longer wires introduce additional capacitance and resistance, which can increase delay and power consumption. Thus, minimizing wirelength is essential for efficient circuit operation.

- Challenges of Routing Congestion: Optimizing routing while avoiding congestion is crucial; congestion can lead to delays and hint at issues during manufacturing, impacting the chip's performance and manufacturability.

- Techniques for Minimizing Wirelength: Engineers employ various techniques, such as advanced algorithms that prioritize shortest paths for signal connections and efficient use of multiple routing layers to spread out connections and minimize bottlenecks.

In summary, wirelength minimization is a foundational concept in the optimization strategies of VLSI physical design, contributing significantly to the overall efficiency, performance, and effectiveness of modern circuits.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Impact on Timing and Power Consumption

Chapter 1 of 1

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Shorter wires reduce delay and power dissipation, so routing algorithms aim to find the shortest possible paths for signals.

Detailed Explanation

The relationship between wirelength, timing, and power consumption is critical in VLSI design. Longer wires naturally have more resistance and capacitance, which adds delay. This means it takes more time for a signal to travel along longer paths, which can slow down the entire circuit operation. Moreover, as electrical current flows through a wire, energy is lost as heat, making longer wires more power-hungry. By minimizing the wirelength, designers can enhance the speed of the circuit and make it more energy-efficient, which is especially important in devices like smartphones and laptops where battery life is crucial.

Examples & Analogies

Think of a marathon: if every runner has to take a long detour to reach the finish line, it will take them longer to complete the race, and they will use up more energy. A shorter, direct path allows them to finish faster and with less fatigue. In VLSI, minimizing wire lengths gives signals a direct route to their destinations, speeding up the operation of the entire circuit and conserving power in the process.

Key Concepts

-

Wirelength Minimization: The goal of reducing the total length of wiring in a circuit to enhance performance and reduce power consumption.

-

Routing Congestion: A challenge characterized by excessive connections in a specific area leading to delays and manufacturing issues.

-

Shortest Path Algorithm: Essential methods used to determine the shortest routing paths between circuit components.

Examples & Applications

In a VLSI design, if a signal travels 10mm through a wire compared to a 5mm wire, the latter would result in lower delay and power consumption.

An advanced routing algorithm implemented successfully reduced wirelength by 30%, thereby enhancing the circuit's overall performance.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Short wires win the race, slower signals lose the chase.

Stories

Imagine a racetrack—cars that drive a shorter path finish quicker and use less fuel. Similarly, shorter wires in circuits lead to faster signal transmissions and lower energy costs.

Memory Tools

Riders in Racing Aren't Lazy (RIRAL) - Remember: Routing Is Relevant to Avoiding Latency.

Acronyms

WAVE - Wires Add to Voltage Excess.

Flash Cards

Glossary

- Wirelength Minimization

A routing optimization strategy aimed at reducing the total length of wires in a circuit, which affects delay and power consumption.

- Routing Congestion

A condition where too many connections are placed in a given area of the chip, leading to potential performance delays and power issues.

- Shortest Path Algorithm

An algorithm that finds the shortest path between two points in a routing layout to minimize wirelength.

- MultiLayer Routing

The use of multiple metal layers to create routing paths in a circuit, allowing for more flexible and less congested connections.

Reference links

Supplementary resources to enhance your learning experience.