Gate Clustering

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Gate Clustering

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're going to discuss gate clustering. Can anyone tell me what they think this might mean?

I think it might have something to do with grouping gates together to save space on the chip.

Exactly! Gate clustering involves grouping gates that are frequently used together into a tighter area on the chip. This reduces the overall area without impacting performance.

How does that help with performance, though?

Great question! By clustering gates, we reduce the wirelength for signal transmission between them, which can enhance speed. This is important because shorter wires lead to quicker signal propagation.

Benefits of Gate Clustering

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

So we've talked about clustering gates. What do you think some benefits of this approach are?

It likely cuts down the overall chip area?

Yes, reducing the chip area directly impacts manufacturing costs. Additionally, it improves power efficiency since shorter connections require less power to drive signals.

Does it also affect timing at all?

Absolutely! Reduced wirelength can also mitigate timing delays, as signals travel faster over shorter distances. Hence, effective gate clustering plays a significant role in timing optimization as well.

Implementation of Gate Clustering

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s shift gears and talk about how we actually implement gate clustering in a design. What do you think is the first step?

Maybe identifying which gates are used together frequently?

Exactly! We analyze the functionality of the circuit to identify these interactions. Once identified, we can strategically place these gates together, forming clusters.

Are there any specific techniques to do this?

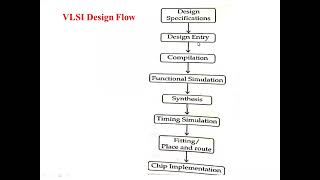

Yes, various algorithms can optimize clustering based on criteria like timing, area, and logical connectivity. This is often part of automated design tools in VLSI.

Limitations and Considerations

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

While gate clustering has its benefits, are there any potential limitations you can think of?

Maybe if the clusters get too big, it could introduce other delays?

That's a good point! Large clusters can lead to increased delays within the cluster. Also, careful attention must be paid to maintain balance; too tight clustering without consideration of performance can hurt timing.

So there's a balance we need to strike?

Precisely! Balancing area reduction with performance and timing is crucial in effective gate clustering. It's all about finding that delicate equilibrium.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses gate clustering, which involves grouping logic gates that are often used together to reduce overall chip area while maintaining performance. By clustering these gates based on their functionality, designers can achieve effective area optimization.

Detailed

Gate clustering is an optimization technique utilized in VLSI physical design to enhance area efficiency. In this technique, gates that frequently interact or are used together in logical operations are grouped into close proximity. This grouping minimizes the total area required for layout while ensuring that performance, timing, and functional integrity are not compromised. Gate clustering is particularly significant as it facilitates reduced wirelength and might contribute to lower power consumption. The process includes analyzing the circuit's functionality, determining the interactions among elements, and creating clusters that maximize efficiency while adhering to design constraints.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Gate Clustering

Chapter 1 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This technique groups gates that are frequently used together into a smaller area.

Detailed Explanation

Gate clustering is a method used in VLSI design to optimize the layout of a circuit. By grouping gates that are frequently activated together into clusters, the overall area that these gates occupy on the chip can be reduced. This is important for saving space and improving efficiency. When several gates work together, clustering them minimizes the distance between them, reducing the space needed for connections (wires) and potentially speeding up performance since the signals can travel faster with shorter paths.

Examples & Analogies

Think of gate clustering like organizing a team of people who need to work together on a project. If they are located close to each other in an office, they can communicate more quickly and effectively, just as clustered gates can transmit signals faster when they are close together. If the team members were scattered across different offices, it would take longer to meet and share ideas, similar to how unclustered gates would take more time for signals to travel between them.

Functionality and Performance Balance

Chapter 2 of 2

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

By clustering gates based on their functionality, area optimization can be achieved without compromising performance.

Detailed Explanation

When gates are clustered together based on how they function, it ensures that they can operate efficiently together while using less space. This approach helps maintain the performance of the circuit because it groups gates that rely on each other's outputs. By organizing these gates efficiently, designers can achieve substantial area savings without sacrificing the speed or capability of the circuit. The challenge is to find the right balance between reducing size and ensuring that the circuit continues to perform well.

Examples & Analogies

Imagine a restaurant kitchen where chefs specializing in different types of cuisine are arranged together. By clustering all the Italian chefs in one area, they can quickly collaborate on dishes that use similar ingredients, enhancing service speed. In the same way, by clustering gates with similar functions, VLSI designers can ensure that connections are made quickly and efficiently, allowing the circuit to run smoothly.

Key Concepts

-

Gate Clustering: A significant optimization technique that groups frequently used gates to minimize chip area.

-

Wirelength Reduction: Achieving shorter connections to enhance performance and reduce power consumption.

Examples & Applications

Example 1: If you have a cluster of AND gates frequently used together in logic operations, grouping them can lead to lesser wirelength and better performance.

Example 2: In a circuit that utilizes flip-flops and specific logic gates, placing them close together based on frequent usage can enhance the chip's layout efficiency.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Cluster the gates, keep them tight, reduce the area, and get it right!

Stories

Imagine a highway where cars (gates) travel from one point to another. If cars are clustered close together, they reach their destination faster with less energy expended, just like in gate clustering!

Memory Tools

GREAT (Grouping Really Enhances Area Tightness) helps remember the goal of gate clustering.

Acronyms

GATE (Group All Together Effectively) summarizes the concept of gate clustering.

Flash Cards

Glossary

- Gate Clustering

A technique in VLSI design that entails grouping logic gates used together to reduce chip area and improve performance.

- Wirelength

The total length of the connections between gates, which impacts signal propagation delay and power consumption.

- Performance Optimization

Strategies aimed at enhancing the speed and efficiency of a circuit's operation.

Reference links

Supplementary resources to enhance your learning experience.