Clock Skew Optimization

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Clock Skew

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today, we're discussing clock skew, which is the arrival time difference of clock signals at various flip-flops. Who can tell me why minimizing clock skew is essential in circuit design?

It's important because different arrival times can cause timing violations.

Exactly! Timing violations can lead to errors in circuit functionality. If clock signals reach some flip-flops earlier than others, we may get incorrect data at the output.

So how do we actually minimize this skew?

Good question! One common technique is clock tree synthesis, which I'll explain further.

Techniques for Minimizing Clock Skew

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s delve into techniques for clock skew optimization. Clock tree synthesis, for instance, helps design a balanced distribution network. What other methods do you think could help?

Maybe adjusting the placement of flip-flops based on their timing requirements?

Precisely! Placement based on timing can significantly reduce skew. We also consider interconnect delays in our calculations to fine-tune the clock distribution.

Are there tools that help in this process?

Yes, indeed! Tools like EDA software provide algorithms for optimizing clock skew while considering all design parameters.

Impact of Clock Skew on Performance

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let’s talk about the performance impact of not optimizing clock skew. What could happen to our circuit?

If the skew is too high, the circuit could fail to operate correctly, right?

Correct! High skew can lead to setup and hold time violations, which can compromise the entire design. Ensuring timely delivery of the clock signal is crucial.

So optimizing clock skew contributes to the overall efficiency of the VLSI circuit?

Exactly! By minimizing clock skew, we improve timing, performance, and overall reliability in our designs.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses the significance of clock skew optimization in VLSI circuit design. By reducing clock skew, designers can prevent timing violations and enhance performance. The discussion includes strategies for achieving this, leading to reliable circuit functionality.

Detailed

In VLSI design, clock skew refers to the time difference in the arrival of the clock signal at different flip-flops within the circuit. Effective clock skew optimization is essential to ensure that all flip-flops receive their clock signals simultaneously, which prevents timing violations and ensures reliable circuit operation. To achieve optimal clock skew, designers may employ various techniques such as clock tree synthesis, which structures the clock distribution network to minimize skew. Optimizing clock skew can significantly enhance the performance of the circuit and maintain synchronization across components. This strategy is particularly critical in high-frequency designs where timing issues can lead to severe functional errors.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Understanding Clock Skew

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Ensuring that the clock signal reaches all parts of the circuit at the same time is critical for timing optimization.

Detailed Explanation

Clock skew refers to the difference in arrival times of the clock signal at various flip-flops (storage elements) in a circuit. If one flip-flop receives the clock signal too late compared to another flip-flop, it can cause timing violations, which may lead to incorrect data being stored or processed. Therefore, it is essential that all parts of the circuit receive the clock signal simultaneously.

Examples & Analogies

Think of clock skew like a relay race where each runner passes the baton to the next runner. If one runner takes longer to receive the baton than the others, the team will fall behind, just like how if one flip-flop gets the clock signal later, it can cause problems in the overall performance of the circuit.

Importance of Minimizing Clock Skew

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Minimizing clock skew can reduce timing violations.

Detailed Explanation

Minimizing clock skew is crucial because it helps ensure that all flip-flops operate in harmony. When clock skew is minimized, the circuit can run at higher clock frequencies without risking data errors, enhancing performance. This reduction aids in maintaining timing constraints such as setup time and hold time, which are essential for reliable operation of sequential elements.

Examples & Analogies

Imagine a conductor leading an orchestra. If the instruments are not playing in sync, the music becomes chaotic. Similarly, in a digital circuit, minimizing clock skew ensures that all parts of the circuit are 'in sync' and functioning correctly within their timing constraints.

Techniques for Reducing Clock Skew

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Several techniques can be employed to minimize clock skew.

Detailed Explanation

To reduce clock skew, designers can use various techniques such as adjusting the placement of flip-flops to ensure equal distances from the clock source, using buffer circuits to strengthen the clock signal, and designing the clock tree structure effectively to distribute the clock signal in a balanced manner. Each of these methods helps to ensure that the clock signal arrives simultaneously at all flip-flops.

Examples & Analogies

Consider a large company where employees are gathered for a meeting. If the meeting starts too early for some employees due to them coming from different locations, the meeting will disrupt the flow. To solve this, employing effective communication and scheduling for every employee to arrive at the same time is analogous to the techniques used to ensure the clock signal reaches all flip-flops simultaneously.

Key Concepts

-

Clock Skew: The timing difference of clock signals received at flip-flops.

-

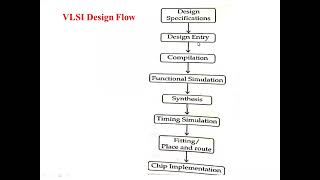

Clock Tree Synthesis: A technique to balance clock signal distribution and minimize skew.

-

Timing Violations: Issues that arise due to differing signal timings.

Examples & Applications

An example of clock skew could be a circuit where one flip-flop receives the clock signal 2 ns later than another, resulting in data capture errors.

In clock tree synthesis, the design ensures that the clock signal reaches all flip-flops within a specified time interval.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

Reduce the skew, sync them all, to keep the function from the fall.

Stories

To win the race, they must start together, ensuring every flip-flop captures data at the right moment.

Memory Tools

SKIP (Synchronize, Keep Even, Install Properly): Remember to synchronize the signals, keep them even, and install proper clock paths to minimize skew.

Acronyms

CLOUT (Clock Layout Optimization and Timing)

Focus on optimizing your clock layout to ensure proper timing.

Flash Cards

Glossary

- Clock Skew

The variation in arrival times of the clock signal at different flip-flops in a circuit.

- Clock Tree Synthesis

A design technique used to create a clock distribution network that minimizes skew.

- Timing Violations

Errors that occur when a flip-flop does not capture the intended data due to incorrect timing.

Reference links

Supplementary resources to enhance your learning experience.