Timing-Driven Routing

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Introduction to Timing-Driven Routing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Today we're going to explore timing-driven routing in VLSI design. Can anyone tell me why timing is important in our circuit layouts?

It's important because if the signals don't arrive on time, the circuit won't function correctly.

Exactly! Timing constraints, such as setup time, hold time, and clock skew, are critical for ensuring that our circuits work as intended. Can someone describe what setup time means?

Setup time is the minimum amount of time before the clock edge that the input data needs to be stable.

Well said! Remembering this can be easy with the mnemonic 'Stable Before Clock'.

What happens if we miss the setup time?

If we miss it, we could have timing violations, causing incorrect data to be latched, which can lead to circuit failures.

In summary, the timing-driven routing process must ensure that critical signals meet their timing requirements while minimizing delays. This is foundational for achieving optimal circuit performance.

Techniques in Timing-Driven Routing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's delve into some key techniques used in timing-driven routing. One common method is route optimization for critical paths. Can anyone explain how we would identify a critical path?

We can identify it by analyzing the delay associated with different paths and determining which one has the longest delay.

Precisely! Optimizing these paths is crucial for ensuring the overall timing constraints are satisfied. What do we mean by signal integrity?

Signal integrity refers to the quality of the electrical signals as they propagate through the circuit. If interference affects them, it can lead to errors.

Correct! Poor signal integrity can lead to issues like crosstalk and delay variation. Therefore, timing-driven routing also involves methods to preserve this integrity.

To summarize, techniques such as optimizing critical paths and ensuring signal integrity are essential to successful timing-driven routing.

Challenges in Timing-Driven Routing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let's talk about some challenges we face in timing-driven routing. Can anyone mention a common obstacle?

Congestion is one of the challenges, I think, because when too many signals are packed into one area, it can create delays.

You're spot on! Routing congestion can indeed lead to timing violations and poor circuit performance. How might we mitigate congestion?

We could use more layers for routing to spread the connections out.

Great idea! Additionally, timing-driven routing algorithms are designed to handle these scenarios by redistributing paths. In summary, being aware of challenges like congestion helps refine our routing strategies.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses timing-driven routing strategies that prioritize meeting timing constraints in circuit layouts. By ensuring critical signals are routed with minimal delay, these strategies enhance performance and maintain signal integrity throughout the design.

Detailed

Detailed Summary

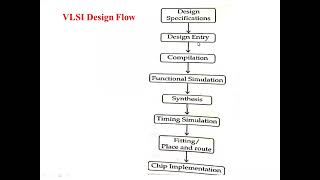

Timing-driven routing is a crucial strategy within the physical design optimization process in VLSI. This approach prioritizes the need to meet specific timing constraints that are essential for functional correctness.

Key aspects of timing-driven routing include:

- Timing Constraints: These are specific requirements such as setup time, hold time, and clock skew, which must be satisfied to ensure the circuit operates correctly at the desired frequency.

- Routing with Minimal Delay: The primary goal is to route signals in a way that minimizes delays, especially for critical paths. Critical paths are those with the longest delays affecting the clock speed. Efficient routing ensures that signals reach their destinations quickly, reducing the overall delay in the circuit.

- Signal Integrity Preservation: Alongside minimizing delays, timing-driven routing ensures that the integrity of the signal is maintained throughout the routing phase. This involves avoiding excessive capacitive loading, inductive coupling, and other forms of interference that can alter signal quality.

Effective timing-driven routing can significantly enhance the performance of the design, allowing for higher clock frequencies and improved overall efficiency.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Overview of Timing-Driven Routing

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing-driven routing focuses on optimizing the layout to meet timing constraints. This involves ensuring that critical signals are routed with minimal delay and that signal integrity is preserved.

Detailed Explanation

Timing-driven routing involves planning the paths that electrical signals take on a chip in such a way that they arrive at their destinations at the right moments. Since electronic circuits operate based on clock signals, it's crucial that the signals reach different components (like gates and flip-flops) precisely when needed. The aim is to minimize any delay that the signals might experience as they travel along the wires, which can affect the circuit's performance. Additionally, preserving signal integrity means ensuring that the signals do not degrade in quality as they move across the routing paths.

Examples & Analogies

Imagine a busy highway system where cars (signals) need to travel from one city (gate) to another during rush hour (the clock cycle). If the cars hit heavy traffic jams (delays), they won't arrive on time, causing a mess (timing violations). Timing-driven routing is like optimizing the routes so that cars can use less congested roads, ensuring they arrive at their destination on time and without accidents (signal degradation).

Critical Signals in Timing-Driven Routing

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This approach ensures that critical signals are routed with minimal delay and that signal integrity is preserved.

Detailed Explanation

In timing-driven routing, particular attention is paid to critical signals—those signals that influence the timing of the entire circuit's operation. Routing these signals efficiently is vital because any delay in critical signals can lead to timing failures. Therefore, methods like minimizing the length of the routing paths, selecting optimal routing layers, and implementing shielding techniques to reduce interference, are employed to ensure these critical paths remain fast and reliable.

Examples & Analogies

Think of critical signals like emergency vehicles needing to reach a destination quickly during a crisis. The routing strategy must ensure they take the fastest and clearest path possible, making use of less congested lanes and adjusting in real-time to avoid roadblocks. Just like those vehicles need a clear route to effectively respond to emergencies, critical signals need optimized routing to ensure the circuit works as intended without glitches.

Preserving Signal Integrity

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Ensuring that critical signals are routed with minimal delay and that signal integrity is preserved.

Detailed Explanation

Preserving signal integrity is about maintaining the quality and strength of signals as they travel through the routing paths. This means avoiding cross-talk (interference from adjacent signals), ensuring that the signals do not weaken over distance, and that they stay stable despite variations in temperature or environmental conditions. Techniques such as using wider traces for critical signals, spacing signals appropriately, and employing ground lines to shield signals from interference are commonly used in timing-driven routing to ensure that signals maintain their form.

Examples & Analogies

Imagine sending a message across a crowded room using a whisper. If there’s too much noise (interference), the person you're trying to reach may not hear you correctly. In the same way, when routing signals on a chip, it's essential to minimize noise and interference so that the signal reaches the destination clearly and effectively. By adjusting how paths are laid out—similar to choosing quieter spots to speak in the room—you can ensure better communication between the components.

Key Concepts

-

Timing Constraints: Parameters like setup time and hold time that must be satisfied.

-

Critical Path: The route that determines the performance limit of the circuit.

-

Signal Integrity: The preservation of the quality of signals along the routing paths.

Examples & Applications

A design that employs timing-driven routing can reduce overall circuit delays, enhancing performance considerably.

When using multiple routing layers effectively, a designer can avoid congestion issues, leading to better signal integrity.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To make signals quick and bright, timing-driven routes are just right.

Stories

Imagine a runner on a track. They must reach the finish line on time (meeting timing constraints); if they get distracted by obstacles (signal integrity issues), they lose the race.

Memory Tools

TCR: Timing, Congestion, Routing - key elements for effective routing.

Acronyms

TIMING

Timing Importance Minimizes In the Next Generation

Flash Cards

Glossary

- TimingDriven Routing

A routing strategy that optimizes the layout to meet specific timing constraints.

- Critical Path

The path that determines the minimum time to complete a circuit, having the longest delay.

- Signal Integrity

The measure of the quality of electrical signals within a circuit to ensure they maintain their intended values.

- Setup Time

The minimum time before the clock edge that input data must be stable for correct latching.

Reference links

Supplementary resources to enhance your learning experience.