Power-Aware Placement and Routing

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Understanding Power Consumption in VLSI

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Welcome everyone! Today we're diving into power consumption in VLSI design. Can anyone tell me why managing power is so crucial?

It's essential for battery-powered devices, right?

Exactly! High power consumption can drain batteries quickly and generate heat. Now let's discuss how we can optimize power through placement and routing.

What do you mean by placement and routing?

Good question! Placement refers to where we position the cells on the chip, and routing is how we connect these cells. Both play a significant role in power efficiency.

How does the placement impact power consumption?

If we can reduce the distance between cells, we also reduce the power needed for connections. That's a core principle in power-aware placement.

So, is there a way to choose cells based on power efficiency?

Certainly! Using low-power cells can significantly lower power usage. Remember, reducing interconnect lengths and thoughtful cell placement are key strategies.

To recap: Minimizing interconnect lengths and selecting low-power cells are essential strategies in power-aware placement and routing.

Techniques in Power-Aware Routing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now, let’s move to routing techniques that can optimize power consumption. What do you think routing involves?

It's about connecting the cells, right?

That's correct! We want to connect them efficiently while keeping power usage low. Can someone give me an example of how routing might affect power?

Longer wires would use more power because of resistance?

Exactly! Long wires can increase power consumption significantly. Thus, our goal is to minimize wire length. What are other factors we should consider in routing?

We should think about capacitance too, right?

Absolutely! Both resistance and capacitance impact power. Therefore, leveraging efficient routing algorithms helps us balance these aspects. Don’t forget: shorter wires mean lower power!

In summary, routing efficiently is about minimizing both distance and capacitive load. It plays a vital role in power-aware designs.

Integration of Techniques for Power Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Finally, how do we bring together placement and routing strategies for effective power optimization?

By making sure low-power cells are located close to each other and considering their connections?

Precisely! A thoughtful approach to both placement and routing ensures minimum power usage. How do we approach this in real designs?

We might use simulation tools to evaluate different configurations?

Exactly! Simulation allows us to iterate and optimize for power consumption effectively.

What’s the trade-off between performance and power though?

Great point! There's always a balance to strike, where optimizing for power can affect performance. Remember, the key is to assess both aspects.

To wrap up, integrating placement and routing techniques is essential for achieving power optimization while maintaining performance levels.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

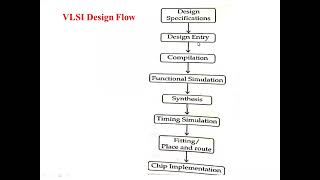

Power-aware placement and routing focuses on minimizing power consumption in VLSI designs by optimizing how cells are placed and how they are interconnected. This includes strategies that balance power efficiency with performance requirements.

Detailed

Power-Aware Placement and Routing

Power-aware placement and routing is a crucial aspect of VLSI design aimed at reducing power consumption while maintaining performance and meeting design constraints. This process involves several strategies:

- Minimize Long Interconnects: Long interconnects can increase power consumption due to greater capacitance and resistance. By optimizing the layout to reduce distances between cells, power efficiency can be significantly improved.

- Utilize Low-Power Cells: Selecting and placing low-power cells strategically can help reduce overall power consumption. Cells designed for low energy usage can be incorporated into critical paths and less critical areas of the design.

- Placement Consideration: The placement of cells should consider not just performance, but also power consumption. By colocating cells with lower power requirements, designers can achieve greater efficiency.

- Routing Optimization: Efficient routing of wires must take into account not only the length but also the impact on power consumption, with careful consideration of interconnections between cells.

The significance of power-aware placement and routing is particularly critical in modern VLSI designs, balancing trends toward higher functionality with the necessity for energy efficiency.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Minimizing Long Interconnects

Chapter 1 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

This technique emphasizes reducing the distance that signals need to travel by minimizing the number of long interconnects.

Detailed Explanation

Long interconnects in a circuit layout can lead to increased power consumption, particularly due to capacitive effects where energy is lost as the signal travels over longer distances. By focusing on minimizing these long interconnects, circuit designers can create more efficient layouts that facilitate shorter signal paths, thus requiring less power to drive signals from one component to another.

Examples & Analogies

Consider a delivery service. The longer the distance that packages must travel, the higher the fuel consumption and time involved. If a delivery service can organize its routes to minimize travel distance, it saves on fuel (power consumption) and ensures quicker delivery times. In circuit design, keeping connections short achieves similar efficiency.

Using Low-Power Cells

Chapter 2 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Employing low-power cells is a fundamental strategy in power-aware placement and routing to significantly lower overall power consumption.

Detailed Explanation

Low-power cells refer to specific circuit components that are designed to operate at reduced voltages or currents while maintaining acceptable performance. Incorporating these cells into the circuit design is vital for minimizing power usage, especially in portable or battery-powered devices. By strategically placing these low-power cells in critical areas of the circuit, designers can further enhance overall energy efficiency.

Examples & Analogies

Think of using energy-efficient light bulbs instead of traditional ones in your home. While both provide light, energy-efficient bulbs consume significantly less electricity. Just like selecting the right light bulbs can reduce your electricity bill, selecting low-power cells can drastically minimize the power consumption of a circuit.

Considering Power Consumption in Placement and Routing Decisions

Chapter 3 of 3

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The process also requires that designers consider power consumption when making decisions about where to place cells and how to route wires.

Detailed Explanation

Power consumption should not just be an afterthought but a fundamental consideration in the placement and routing process. Designers must weigh the power implications of their choices, aiming to optimize the layout such that energy is conserved without sacrificing performance. This might involve choosing locations for certain components based on their power profiles, and deciding on routing pathways that help reduce power loss.

Examples & Analogies

This is like planning a road trip where fuel efficiency is a top priority. Instead of taking the easiest or quickest route, you might choose a more energy-efficient path that, while it might take slightly longer, saves you money on gas. Just as a smart road trip requires careful planning of route and stops based on fuel consumption, effective circuit design requires thorough consideration of power consumption in every placement and routing decision.

Key Concepts

-

Power Consumption: The amount of energy used by the circuit during operation.

-

Cell Placement: The strategy of arranging functional units within a chip to optimize for power and performance.

-

Routing Efficiency: The process of minimizing distances and load in circuit connections to enhance power performance.

-

Low-Power Design: Design strategies aimed at reducing the overall energy footprint of circuits.

-

Signal Integrity: Maintaining the quality of electrical signals during transmission, which can be affected by routing.

Examples & Applications

In a mobile phone design, using low-power cells can help extend battery life significantly.

By placing frequently interconnected components close together, such as a processor and memory, designers can minimize power-hungry interconnections.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

When cells are placed with care and thought, energy savings are easily sought.

Stories

Imagine a city where all the houses are connected by the shortest roads, reducing traffic jams. Similarly, in a chip, keeping components close reduces power draw.

Memory Tools

PLOW: Placement, Length reduction, Optimization, Wires – key strategies for power-aware design!

Acronyms

POWER

Placement of Optimal low-power cells With Efficient routing.

Flash Cards

Glossary

- Placement

The process of positioning cells within a chip layout to optimize performance and power.

- Routing

The interconnection of cells using metal traces to form a complete circuit.

- LowPower Cells

Transistor cells designed to consume minimal power during operation.

- Interconnect Length

The distance between connected components, significant in determining power consumption.

- PowerAware Design

An approach that considers power consumption at all stages of VLSI design.

Reference links

Supplementary resources to enhance your learning experience.