Timing Optimization Strategies

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Critical Path Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's begin with critical path optimization. The critical path is the longest delay path in the circuit. Do anyone know why optimizing this path is essential?

I think it's because it affects the maximum clock frequency we can have.

Exactly! By reducing the delays in the critical path, we can increase the overall speed of our circuit. We can achieve this through methods like gate resizing and logic restructuring. Who can tell me how gate resizing can help?

Larger gates can switch faster, right? But they take up more space.

Right! It’s a trade-off between performance and area. Remember the acronym 'GPT' for 'Gate Performance Trade-off'.

Got it, GPT helps me remember the balance!

Great! So, optimizing the critical path is essential to improve the clock frequency. Let’s summarize…

To recap, reducing delays on the critical path affects our circuit's speed, done through techniques like gate resizing and logic restructuring. Always remember GPT!

Retiming

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next, let’s discuss retiming. Who knows what this technique involves?

It’s about moving flip-flops around in the circuit to optimize timing, right?

Yes! Retiming adjusts where flip-flops are located along the critical path, which can help balance delays. Why do you think this is necessary?

It reduces overall delay without changing the design functionality.

Exactly! And we can think of it like rearranging furniture for the best flow in a room—a perfect analogy! Any questions about this process?

Is there a limit on how many times we can retime?

Good question! While there isn't a strict limit, excessive retiming can lead to complexity and congestion in the circuit. Let’s summarize…

In summary, retiming helps in balancing delays in a design without changing functionality, much like rearranging furniture to create a better space flow.

Pipelining

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let's delve into pipelining. Who can tell me what pipelining involves?

Isn't it about splitting tasks into smaller steps with additional flip-flops?

Exactly right! Pipelining breaks long combinational paths into smaller stages, improving performance. What’s a downside of this?

It increases area and power consumption?

Correct! We need to balance performance improvements with area and power. Let’s use the mnemonic 'SPAP'—Split, Performance, Area, Power—to remember this balance.

That’s easy to recall, SPAP!

Great! As a final summary, remember that pipelining improves performance by dividing tasks but requires careful consideration of the trade-offs regarding area and power.

Clock Skew Optimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Our last topic is clock skew optimization. What do you know about clock skew?

It’s the variation in arrival times of the clock signal to different parts, right?

Yes! Minimizing clock skew is crucial to avoid timing violations. Can anyone explain why it matters?

If the clock doesn’t arrive simultaneously, it can lead to incorrect operations or timing errors?

Correct! Let’s remember 'CTZ'—Clock Timing Zone—as a memory aid for understanding clock skew's critical nature.

I like that! CTZ is easy to link to clock issues.

Excellent! Let's summarize today’s lesson…

In summary, clock skew optimization ensures timely arrival of clock signals across the design, crucial for avoiding errors. Remember CTZ for its importance!

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

This section discusses various timing optimization strategies such as critical path optimization, retiming, pipelining, and clock skew optimization. These techniques are essential for meeting design requirements related to setup time, hold time, clock skew, and propagation delays, ultimately enhancing circuit performance.

Detailed

Timing Optimization Strategies

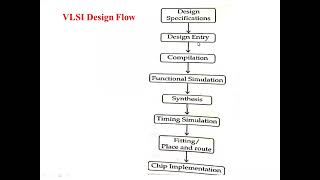

Timing optimization in VLSI designs plays a crucial role in ensuring that all timing requirements are met, thus guaranteeing the correct operation of the circuit. Various strategies are employed to achieve this, each targeting specific timing aspects:

- Critical Path Optimization: The critical path is the longest path of the circuit, which determines the maximum operating frequency. Techniques such as gate resizing, retiming, and logic restructuring are essential in minimizing delays along this path, thereby improving performance.

- Retiming: This technique involves adjusting the position of flip-flops within the design. By redistributing the timing elements, retiming can reduce the overall delay without impacting functionality, effectively optimizing performance.

- Pipelining: Pipelining separates long combinational paths into shorter, manageable stages by introducing additional flip-flops. While this increases clock frequency and improves overall speed, it requires careful balancing due to the increase in area and power consumption that results.

- Clock Skew Optimization: Optimizing clock skew—variations in arrival times of the clock signal—is critical. Balanced arrival ensures that all parts of the circuit receive the clock signal simultaneously, minimizing potential timing violations and enhancing reliability.

Timing optimization strategies are integral for modern VLSI designs, influencing both the performance and functional reliability of integrated circuits.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Introduction to Timing Optimization

Chapter 1 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing optimization ensures that the design meets the required timing constraints, such as setup time, hold time, clock skew, and propagation delays. These constraints must be satisfied to ensure the correct functionality of the circuit.

Detailed Explanation

Timing optimization focuses on ensuring that various timing-related issues in a circuit are addressed to guarantee proper operation. Important timing constraints include setup time, which is the time before a clock edge that data must be stable; hold time, the time after a clock edge that data must remain stable; clock skew, which is the difference in arrival times of the clock signal to different parts of a circuit; and propagation delay, the time taken for a change in input to affect the output. Meeting these constraints is essential for the circuit to function as intended.

Examples & Analogies

Think of timing optimization like making sure a race starts at the same time for all runners. If one runner gets the signal to start sooner or later than others (like clock skew), it could affect the outcome of the race. Similarly, in electronics, if signals do not meet their timing constraints, the circuit may not work correctly.

Critical Path Optimization

Chapter 2 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

The critical path determines the maximum clock frequency of the design. Optimizing the critical path by reducing delays in timing-critical regions improves the performance of the design. This can be achieved through techniques such as gate resizing, retiming, and logic restructuring.

Detailed Explanation

The critical path is the longest path that signals take through the circuit, determining how fast the entire circuit can operate, often referred to as the maximum clock frequency. By focusing on optimizing this path through methods like gate resizing (adjusting the size of gates to speed them up), retiming (moving flip-flops to optimize delays), and logic restructuring (changing how logic gates are arranged), the performance of the design can be significantly improved.

Examples & Analogies

Imagine a relay race where one runner is slower than others. To improve the team's performance, you could change the order of runners to place the slower runner in a position where they have to run less distance or support them with a stronger teammate. In circuits, focusing on the critical path achieves a similar effect by improving the slowest parts of the design.

Retiming

Chapter 3 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Retiming involves shifting flip-flops along the critical path to balance delays and reduce the overall timing of the design. By redistributing the registers, the timing of the circuit can be optimized without changing its functionality.

Detailed Explanation

Retiming is a strategy used to optimize circuit timing by adjusting the positions of flip-flops along the critical path. By moving these registers without altering their logical connections, you can balance delays among different paths, ultimately resulting in a faster design without modifying its output. This technique ensures that data moves through the circuit more efficiently, reducing the overall time it takes for signals to propagate.

Examples & Analogies

Consider a production line where workers are responsible for assembling different parts of a product. If one worker is slower and holds up the entire line, the manager can move faster workers to help balance the workload, speeding up the overall process without changing what each worker is doing. Similarly, retiming helps to balance circuit workloads and enhance performance.

Pipelining

Chapter 4 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Pipelining breaks long combinational paths into smaller stages by adding additional flip-flops. This can increase the clock frequency and improve performance. However, it also increases area and power consumption, so a balance must be maintained.

Detailed Explanation

Pipelining is a technique used to improve the performance of a circuit by dividing long processing paths into shorter stages, with each stage being followed by flip-flops that store the interim results. This allows for a new set of data to be processed while the previous data is still being worked on, effectively increasing the circuit's throughput and allowing for higher clock frequencies. However, introducing more flip-flops can lead to increased area on the chip and higher power consumption, requiring careful consideration in design.

Examples & Analogies

Imagine an assembly line in a factory where items are passed down several stations to complete production. If each station can work on its task concurrently instead of waiting for the entire item to finish, production becomes more efficient. This is similar to how pipelining allows a circuit to process multiple data sets at once, enhancing overall performance.

Clock Skew Optimization

Chapter 5 of 5

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Ensuring that the clock signal reaches all parts of the circuit at the same time is critical for timing optimization. Minimizing clock skew, which is the difference in arrival times of the clock signal at various flip-flops, can reduce timing violations.

Detailed Explanation

Clock skew refers to the variation in the arrival times of the clock signal at different flip-flops in a circuit. For circuits to function correctly, the clock signal must arrive simultaneously at all components. If it doesn't, some parts of the circuit may operate based on outdated information, leading to timing violations. Reducing clock skew through careful routing and design choices helps ensure that timing constraints are satisfied, improving circuit reliability and performance.

Examples & Analogies

Consider a synchronized swimming team performing a routine. If some swimmers hear the music or cues at different times, the performance may appear chaotic and uncoordinated. Ensuring that all team members start at the same moment, just like minimizing clock skew, leads to a flawless and synchronized performance.

Key Concepts

-

Critical Path: It determines the maximum frequency of the circuit.

-

Retiming: Shifting flip-flops helps balance delays without changing functionality.

-

Pipelining: Dividing tasks into smaller stages improves performance at the cost of area.

-

Clock Skew: Minimizing clock skew ensures consistent timing across the circuit.

Examples & Applications

In a circuit with multiple stages, altering the placement of flip-flops can reduce the overall delay while maintaining the circuit's functionality.

In a pipelined architecture, instructions can execute simultaneously in different stages, increasing throughput without requiring a clock frequency increase.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

In designs where timing's key, critical paths must be free; optimize to increase speed and balance is what we need.

Stories

Imagine a race where one runner always trips. By shifting their position, they run smoother and faster, just like how retiming works in circuits!

Memory Tools

Remember SPAP for Pipelining: Split the task, Performance Boost, Area Increase, Power Caution.

Acronyms

Use CTZ for Clock Skew

Clock Timing Zone—ensure timing is synchronized across zones.

Flash Cards

Glossary

- Critical Path

The longest path in a circuit, determining the maximum clock frequency.

- Retiming

The process of shifting flip-flops to adjust delays within the circuit.

- Pipelining

A technique that divides long combinational paths into shorter stages to improve performance.

- Clock Skew

The difference in arrival times of the clock signal at various circuit components.

Reference links

Supplementary resources to enhance your learning experience.