Routing Optimization Strategies

Enroll to start learning

You’ve not yet enrolled in this course. Please enroll for free to listen to audio lessons, classroom podcasts and take practice test.

Interactive Audio Lesson

Listen to a student-teacher conversation explaining the topic in a relatable way.

Wirelength Minimization

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Let's start with wirelength minimization. Why do you think it's crucial in routing optimization?

Because shorter wires can reduce delays and power consumption?

Exactly! In VLSI design, minimizing wirelength helps achieve lower power dissipation. Remember, less distance equals less resistance. Can anyone think of how we might achieve this?

We can use algorithms to find the shortest paths?

Right! There are specialized routing algorithms designed for this. Now, can you recall an acronym that helps us remember the benefits of wirelength minimization? Hint: FAP.

FAP? Does it stand for Faster, Accurate, and Power-efficient?

Great memory! Now, let's summarize. Minimizing wirelength leads to faster operation and less power usage, which reinforces why it's vital in routing optimization.

Congestion Management

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Congestion management is our next topic. What do we mean by routing congestion?

Isn't it when too many signals are trying to use the same area?

Exactly. It can lead to increased delays and power consumption. What strategies do you think we could use to manage this?

We could balance the wire distribution?

Absolutely! Balancing the distribution of wires helps alleviate congestion. Can someone explain why this is crucial for design?

It reduces delays and improves the reliability of the circuit.

Well said! To sum up, effective congestion management enhances performance and reliability, which is critical in our designs.

Multi-Layer Routing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Next up is multi-layer routing. Why do you think using multiple layers can be beneficial?

It gives us more options for connecting signals without causing congestion!

Correct! Utilizing multiple layers allows for efficient resource allocation and can help maintain signal integrity. Who can share an example of when this might be applied?

In complex designs where many interconnections are needed?

Exactly! Multi-layer routing is especially beneficial in complex VLSI layouts. Let’s recap: multiple layers enhance flexibility and help manage congestion effectively.

Timing-Driven Routing

🔒 Unlock Audio Lesson

Sign up and enroll to listen to this audio lesson

Now let’s talk about timing-driven routing. Why is timing important in routing?

To ensure that signals arrive on time and maintain performance?

Exactly! Timing-driven routing helps optimize the layout so that critical signals meet their timing constraints. What are some methods we might use to implement this?

Ensuring that critical paths are prioritized in the routing process?

Great insight! Prioritizing critical signals can greatly impact performance. Finally, how would you summarize the importance of timing-driven routing?

It improves performance and ensures that the design functions correctly under timing constraints.

Well put! Remember, meeting timing constraints is essential for the success of any VLSI design.

Introduction & Overview

Read summaries of the section's main ideas at different levels of detail.

Quick Overview

Standard

Routing optimization is crucial in VLSI physical design as it directly influences chip performance metrics such as timing and power consumption. Key strategies include minimizing wirelength, managing congestion, utilizing multi-layer routing, and implementing timing-driven routing to enhance overall design efficiency.

Detailed

Routing Optimization Strategies

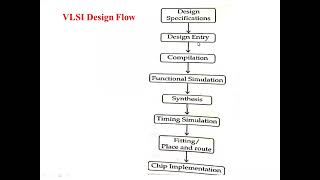

Routing optimization is a critical component of VLSI physical design, as this process involves connecting various cells and blocks with metal traces on the chip. Effectively optimizing routing can significantly boost the performance of a chip by minimizing wirelength, reducing congestion, and ensuring improved signal integrity. The primary strategies in routing optimization are:

Key Strategies:

- Wirelength Minimization: A crucial goal of routing is to minimize wirelength, as shorter wires lead to reduced delay and power dissipation. Efficient routing algorithms strive to find the shortest paths for signals.

- Congestion Management: Routing congestion can hinder performance due to excessive connections in certain areas, resulting in delays and increased power usage. Effective routing strategies aim to alleviate congestion by balancing wire distribution.

- Multi-Layer Routing: Implementing multiple layers of metal interconnects allows for greater flexibility in routing. Multi-layer routing helps reduce congestion and maintain signal integrity through optimized resource allocation across layers.

- Timing-Driven Routing: This approach focuses on meeting timing constraints effectively. Timing-driven routing ensures that critical signals are connected with low delay and signal integrity is upheld, ultimately leading to improved performance.

In summary, these routing optimization strategies contribute to a more efficient VLSI design, ultimately satisfying the increasing demands for performance and power efficiency in modern circuit design.

Youtube Videos

Audio Book

Dive deep into the subject with an immersive audiobook experience.

Wirelength Minimization

Chapter 1 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

One of the main goals in routing is to minimize wirelength, which directly affects both timing and power consumption. Shorter wires reduce delay and power dissipation, so routing algorithms aim to find the shortest possible paths for signals.

Detailed Explanation

Wirelength minimization is a fundamental aspect of routing in VLSI circuit design. The aim is to keep the connecting wires (or traces) as short as possible. This is crucial because longer wires can introduce delays in signal transmission and increase power consumption, negatively impacting the circuit’s performance. In essence, when we minimize the distance signals must travel, we help ensure that the circuit operates swiftly and efficiently.

Examples & Analogies

Imagine trying to send a letter. If you can send it directly to your friend next door, it will arrive much faster than if you have to send it across the country. Similarly, in circuit design, minimizing the length of communication paths ensures faster signal delivery and lower energy usage.

Congestion Management

Chapter 2 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Routing congestion occurs when there are too many connections in a given area of the chip, leading to timing delays, increased power consumption, and manufacturing challenges. Optimizing routing to avoid congestion and balance the distribution of wires is crucial.

Detailed Explanation

Congestion management addresses the challenges that arise when there are excessive connections in a limited area on the chip. When too many wires cross over each other or are packed closely together, it can lead to problems. These include delays in signal transmission, higher power usage, and complications during manufacturing due to increased chances of errors. By ensuring that the routing is well-balanced and avoiding congestion, we enhance the reliability and efficiency of the circuit.

Examples & Analogies

Think of a busy highway during rush hour where too many cars are trying to merge into a single lane. This causes traffic jams and delays. However, if we can manage these cars, perhaps by creating more lanes or directing them into less congested routes, travel time can be reduced significantly. Similar strategies in routing involve distributing connections evenly to prevent bottlenecks.

Multi-Layer Routing

Chapter 3 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Using multiple layers of metal interconnects allows for more flexible routing options and can reduce congestion. Efficient multi-layer routing algorithms allocate resources across different layers to minimize congestion while maintaining signal integrity.

Detailed Explanation

Multi-layer routing involves using several layers of conductive materials (metal interconnects) to connect different parts of the circuit. By allowing connections to be placed on different levels, we gain greater flexibility in routing, akin to multiple paths in three-dimensional space. This method helps alleviate congestion, as more connections can be accommodated without interfering with each other. Furthermore, advanced algorithms optimize how these layers are utilized to ensure that signals are transmitted effectively without integrity loss.

Examples & Analogies

Consider a multi-story parking garage. Instead of having all cars on a single level, spreading them across multiple levels allows for better management of space and reduces the chances of congestion. Just like this garage allows for more cars, multi-layer routing enables more connections without overcrowding one layer.

Timing-Driven Routing

Chapter 4 of 4

🔒 Unlock Audio Chapter

Sign up and enroll to access the full audio experience

Chapter Content

Timing-driven routing focuses on optimizing the layout to meet timing constraints. This involves ensuring that critical signals are routed with minimal delay and that signal integrity is preserved.

Detailed Explanation

Timing-driven routing is a specialized approach to ensure that important signals in the circuit reach their destinations on time. In a circuit, certain signals are designated as 'critical' because delays in their transmission can directly affect overall performance. This method prioritizes the paths of these critical signals to be as fast as possible while also safeguarding against interference and maintaining integrity. The balance between speed and accuracy is crucial in achieving efficient circuit operation.

Examples & Analogies

Think of a relay race where passing the baton quickly and accurately is essential for winning. If one runner delays the baton handoff, the team can lose the race. Similarly, timing-driven routing ensures that the critical signals pass through their paths without delay and with precision to keep the circuit running optimally.

Key Concepts

-

Wirelength Minimization: A strategy for reducing wire connections' length to enhance performance.

-

Congestion Management: Techniques to alleviate routing congestion in VLSI designs.

-

Multi-Layer Routing: Utilizing multiple layers for a flexible routing approach.

-

Timing-Driven Routing: An approach focused on meeting timing constraints in circuit design.

Examples & Applications

In high-performance CPUs, wirelength minimization is crucial to reduce delays in signal propagation.

Congestion management is vital in large FPGAs where multiple connections can lead to significant performance degradation.

Multi-layer routing allows for advanced packaging technologies that can accommodate numerous signals without sacrificing performance.

Timing-driven routing is used in critical path optimization to ensure timely delivery of signals across components.

Memory Aids

Interactive tools to help you remember key concepts

Rhymes

To wires that run long, delay and power are strong.

Stories

Imagine a busy highway (congestion); when there are too many cars trying to drive through one lane, traffic jams happen. Multi-layer routing acts as extra lanes, allowing smooth flow of vehicles (signals).

Memory Tools

Remember the acronym WCM-T (Wirelength, Congestion, Multi-layer, Timing) to recall key routing optimization strategies.

Acronyms

COW (Congestion, Options (Multi-layer), Timing) helps remember the routing priorities.

Flash Cards

Glossary

- Wirelength Minimization

The strategy of reducing the length of wire connections in a circuit layout to decrease delay and power consumption.

- Congestion Management

Techniques used to alleviate excessive routing connections in a specific area, reducing delays and improving circuit performance.

- MultiLayer Routing

A method that utilizes multiple metal layers for routing connections, allowing for more efficient signal distribution and reduced congestion.

- TimingDriven Routing

Routing approach that prioritizes timing constraints to ensure that critical signals meet performance criteria.

Reference links

Supplementary resources to enhance your learning experience.